# UNIVERSITY BIRMINGHAM University of Birmingham Research at Birmingham

# Real-Time FPGA-RTDS Co-Simulator for Power Systems

Yang, Conghuan; Xue, Ying; Zhang, Xiao-ping; Zhang, Yi; Chen, Yuan

DOI: 10.1109/ACCESS.2018.2862893

*License:* Creative Commons: Attribution (CC BY)

Document Version Publisher's PDF, also known as Version of record

Citation for published version (Harvard):

Yang, C, Xue, Y, Zhang, X, Zhang, Y & Chen, Y 2018, 'Real-Time FPGA-RTDS Co-Simulator for Power Systems', *IEEE Access*, vol. 6, pp. 44917-44926. https://doi.org/10.1109/ACCESS.2018.2862893

Link to publication on Research at Birmingham portal

Publisher Rights Statement: Published in IEEE Access on 03/08/2018

(c) 2018 IEEE

#### **General rights**

Unless a licence is specified above, all rights (including copyright and moral rights) in this document are retained by the authors and/or the copyright holders. The express permission of the copyright holder must be obtained for any use of this material other than for purposes permitted by law.

•Users may freely distribute the URL that is used to identify this publication.

•Users may download and/or print one copy of the publication from the University of Birmingham research portal for the purpose of private study or non-commercial research.

•User may use extracts from the document in line with the concept of 'fair dealing' under the Copyright, Designs and Patents Act 1988 (?) •Users may not further distribute the material nor use it for the purposes of commercial gain.

Where a licence is displayed above, please note the terms and conditions of the licence govern your use of this document.

When citing, please reference the published version.

#### Take down policy

While the University of Birmingham exercises care and attention in making items available there are rare occasions when an item has been uploaded in error or has been deemed to be commercially or otherwise sensitive.

If you believe that this is the case for this document, please contact UBIRA@lists.bham.ac.uk providing details and we will remove access to the work immediately and investigate.

Received June 23, 2018, accepted July 25, 2018, date of publication August 3, 2018, date of current version September 5, 2018. *Digital Object Identifier* 10.1109/ACCESS.2018.2862893

# **Real-Time FPGA-RTDS Co-Simulator for Power Systems**

CONGHUAN YANG<sup>1</sup>, YING XUE<sup>1</sup>, (Member, IEEE), XIAO-PING ZHANG<sup>10</sup>, (Senior Member, IEEE), YI ZHANG<sup>2</sup>, (Senior Member, IEEE), AND YUAN CHEN<sup>2</sup>

<sup>1</sup>Department of Electronic, Electrical and Systems Engineering, University of Birmingham, Birmingham B15 2TT, U.K. <sup>2</sup>RTDS Technologies Inc., Winnipeg, MB R3T 2E1, Canada

Corresponding author: Xiao-Ping Zhang (x.p.zhang@bham.ac.uk)

This work was supported by EPSRC under Grant EP/M002845/1, Grant EP/L017725/1, and Grant EP/N032888/1.

**ABSTRACT** This paper proposes a co-simulation platform using field-programmable gate array (FPGA) and real-time digital simulator (RTDS) for the simulation of large power systems. It combines the advantages of high computational power from FPGA and better modelling flexibility from RTDS together. The FPGA therefore acts as an efficient and economical extension to RTDS especially when simulating large ac systems. One of the significant advantages of the proposed co-simulator is that it avoids the potential interface error existing in the conventional approach of interfacing transient stability program with electromagnetic transient programs. Two key aspects of the proposed co-simulator are discussed: 1) the interface design between FPGA and RTDS and 2) the hardware implementation and expandability of the platform. Two case studies are presented to verify the simulation accuracy and capability of the proposed co-simulator. The first case simulates a two-area four-machine power system with one area simulated in RTDS. The second case simulates a system of 141 buses in FPGA to demonstrate the simulator's capability in simulating large power systems.

**INDEX TERMS** Electromagnetic transients, field- programmable gate array (FPGA), real-time digital simulator (RTDS), power system simulation.

#### **I. INTRODUCTION**

Modern electrical power systems are undergoing dramatic changes such as:

- Increasing amount of renewable energy integration;

- Increasing level of interconnections between regional/national electrical power systems [1];

- Increasing applications of power electronic devices in existing AC networks [2].

All these changes result in an increase in size and complexity of power systems. In particular the application of power electronic devices introduces a range of new risks which are different in nature to those in traditional AC power systems. For example they could affect the operation of protection relays [3], cause harmonic problems [4] or control interactions [5], and lead to potential overvoltage/overcurrent problems. Real-Time Simulation (RTS) using Electromagnetic Transient (EMT) type of component models is essential and has been widely used to study these problems [6], [7].

One of the main difficulties for RTS is that significant computational resources are required for the solution of detailed EMT models thereby limiting the size of AC system that can be accurately simulated [6]. One of the conventional methods in simulating larger system is to use network equivalents, which neglects internal dynamics of the equivalent part of the system. To increase the size of system that can be simulated while maintaining simulation accuracy, hybrid simulation combining EMT and Transient Stability (TS) programs was proposed [8], [9]. This method partitions the whole system into two or more subsystems. The area/areas with power electronic devices is/are simulated accurately using EMT programs. The rest of the network is simulated using TS programs to save computational resources. The accuracy and efficiency of hybrid simulation critically depend on the interface technique [8]. Therefore most of the previous works are focusing on the design of interface between TS and EMT subsystems.

Conventionally the fundamental frequency equivalent of the TS subsystem is adopted [10] and both positive-sequence and three-sequence equivalent models are used [11]-[13]. The drawback of using positive-sequence network is that it will give inaccurate results for unbalanced conditions [11]. To mitigate the problem, significant extension of the interface bus was proposed to maintain the assumption of three-phase balance, but simulation efficiency of EMT part is significantly reduced [13]. For three-sequence equivalent model, the representation may not be accurate when the transients at interface buses are significant [10]. The Frequency-Dependent Network Equivalent (FDNE) was recently proposed in [10] to decrease the interface error. A number of approaches to obtain the FDNE are proposed [14], [15], and different representations of FDNE are adopted [16]. The main disadvantages of these methods are the increased computational burden on the EMT simulator and potential inaccuracy under transient conditions.

It is understandable that the design of an interface technique that is accurate and computationally efficient is difficult, as these two simulation methods have fundamentally different mathematical models.

This paper proposes a real-time FPGA-RTDS co-simulator using EMT models only, hence avoiding the complexities in interface design and the potential interface errors exist in hybrid simulation methods. At the same time, the size of the power system that can be simulated is not compromised as a large part of the network can be simulated using FPGA taking advantage of its computational power. The rest part of the network of interest is simulated using RTDS taking advantage of its simulation flexibilities.

It needs to be mentioned that the EMT simulation of large AC network has been implemented using FPGA in [17]–[19]. However, the method lacks Graphical User Interface (GUI) for the manipulation of simulation cases and visualization of results. Also the control systems for synchronous generators (excitation system and governor system) are not modelled. Other works have been focusing on the simulation of power electronic devices with small simulation time-step using FPGA [20], [21]. In those works, FPGA is used to simulate the detailed model of Modular Multilevel Converter (MMC). One of the difficulties in implementing those methods is to avoid re-synthesize of FPGA (which can take hours) whenever system modification (frequent in simulating power electronic systems) is required. Also the development of a generic model for power electronic device in FPGA can be complex as many of the power electronic devices are still evolving with changing topologies, control strategies and modelling approach [22], [23].

Different from these methods, the proposed method utilizes FPGA to simulate large AC networks rather than power electronic systems, taking advantages of the well-established EMT models of AC components [24], [25]. In addition, the flexibility in system reconfiguration, modelling and control that are readily available in RTDS can be utilized. The role of FPGA therefore is to act as an efficient extension

44918

to RTDS in simulating large-sized AC networks without losing model accuracy and with no interface errors, while the configuration of the system and results visualization are conveniently carried out using RTDS.

This paper is organized as follows. Section II introduces the EMT models of power system components and the modelling of controllers for synchronous machines. Section III introduces the architecture of the co-simulator. The design of interface between FPGA and RTDS is discussed. Section IV explains the hardware implementation of the AC system. Discussion on the expandability of the model in FPGA is presented. Section V shows the results of two simulation case studies to verify the accuracy and simulation capability of the proposed co-simulator. Section VI discusses the relationship between the size of network to be simulated and the hardware resource utilization & minimum simulation time-step. Finally Section VII concludes the paper.

# II. EMT MODELS OF POWER SYSTEM COMPONENTS & CONTROLLERS

To correctly simulate the dynamic behavior of AC power systems, it is essential that both the power system components and the control systems for synchronous machines are modelled in detail.

### A. POWER SYSTEM COMPONENTS

### 1) SYNCHRONOUS GENERATOR

The Universal Machine (UM) model [26] for synchronous generator is adopted. It is a generalized machine model that can be used to represent different types of rotating machines for EMT studies. One *d*-axis damper winding and two *q*-axis damper windings are modelled for each machine. The dynamic equations describing the electrical and mechanical parts of the synchronous generator are shown in equation (1)-(3):

$$v_{dq0} = -Ri_{dq0} + \frac{1}{\omega_{base}} \frac{d\lambda_{dq0}}{dt} + u \tag{1}$$

$$\lambda_{dq0} = Li_{dq0} \tag{2}$$

$$T_m = 2H\frac{d\omega_r}{dt} + D\omega_r + T_e \tag{3}$$

where  $v_{dq0}$ ,  $i_{dq0}$ ,  $\lambda_{dq0}$  and u are vectors of stator dq0 voltage and excitation voltage, dq0 winding currents, dq0 flux linkages and speed voltage terms due to the dq0 transformation. R is the resistance matrix consisting of resistance values of stator, rotor and damper windings. L is a symmetrical matrix consisting of self, mutual and leakage inductances of the machine.  $T_m$ ,  $T_e$ ,  $\omega_r$ ,  $\omega_{base}$ , D, H are mechanical torque, electrical torque, rotor angular frequency, rated angular frequency, damping torque constant and per unit inertia of rotor. All variables in (1) to (3) are in per unit except time, which is in second. The positive direction of stator current is flowing out of the machine.

To facilitate model implementation using FPGA, (1)-(3) are discretized according to the rule of trapezoidal integration and is realized by 6 sub-modules in the actual FPGA hardware implementation as will be shown in yellow blocks in Fig.6 and Fig.13. It should be mentioned that the calculations of  $v_{dq0}$  in step 3 and  $i_G$  in step 5 share the same hardware module as they are both performing the transformation between *abc* and *dq0* reference frames. The descriptions of these sub-modules and the parallelism between them are provided in Section IV.

#### 2) TRANSMISSION LINE

The distributed parameter transmission line model is adopted, which is solved in modal domain before converting back to phase domain. The hardware implementation of the model consists of 2 submodules: phase/modal transformation module and transmission line solver. The transformation module converts all relevant voltages and currents from phase domain to modal domain for calculation, and converts the results from modal domain back to phase domain after solution.

# 3) PASSIVE ELEMENTS

Trapezoidal rule of integration is utilized to discretize the dynamic equations for inductors and capacitors. As a result, all system inductors and capacitors are represented as the parallel connection of history current terms and constant impedance [24]. The history currents are directly used by the "Nodal Equation Solver" described later to calculate the system nodal voltages.

# 4) FAULTS

Fault changes the network admittance matrix and system equivalent resistance. In the proposed EMT co-simulator, these matrices are pre-stored and are chosen according to the fault scenarios. As discussed in previous section, most of the fault cases are implemented using RTDS taking advantage of the flexibility of its GUI.

# B. CONTROL SYSTEMS FOR SYNCHRONOUS MACHINES1) EXCITATION SYSTEM

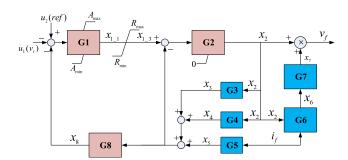

For demonstration purpose, IEEE Type AC1A excitation system [27] is modelled to control the terminal voltage of synchronous generator. The block diagram representation of excitation system is shown in Fig. 1 where  $u_1$ ,  $u_2$ ,  $v_f$ ,  $i_f$  are reference voltage, measured terminal voltage, field excitation

FIGURE 1. Block diagram representation of AC1A excitation system.

voltage and field excitation current. The rest are internal variables to the excitation system itself. Once G1-G8 are discretized according to the trapezoidal rule of integration, the FPGA module computes the value of  $v_f$  for next time-step using the calculated terminal voltages of  $v_d$  and  $v_q$  from this time-step.

#### 2) GOVERNOR/TURBINE SYSTEM

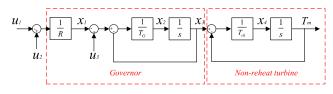

For the purpose of demonstration, the governor/turbine system as shown in Fig. 2 is simulated using FPGA.  $u_1$  is the speed reference,  $u_2$  is the measured rotor speed,  $u_3$  is the load set point,  $x_1$  to  $x_4$  are internal variables and  $T_m$  represents the mechanical torque in per unit. I/R represents the percentage of droop,  $T_G$  is the time constant of governor and  $T_{ch}$  is the time constant of main inlet volumes and steam chest. Similar to the excitation system, the complete governor/turbine system is discretized for implementation in FPGA. The mechanical torque for synchronous machine at next time-step is calculated using the rotor speed, value of  $x_3$  and value of mechanical torque from last time-step.

FIGURE 2. Governor/Turbine System.

# C. NODAL EQUATIONS SOLVER

Synchronous machines are solved separately from the linear parts of the system due to its nonlinearity. Compensation method [25] is used to provide the interface between them. It calculates the Thevenin equivalent of the linear part of the system and solves the machine terminal current. The machine is then represented as a current source for the solution of whole network using the formulated nodal voltage equations.

### **III. ARCHITECTURE OF THE CO-SIMULATOR**

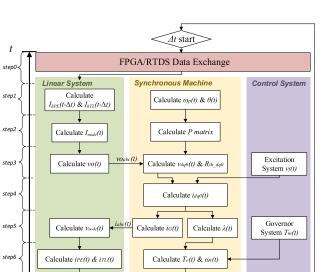

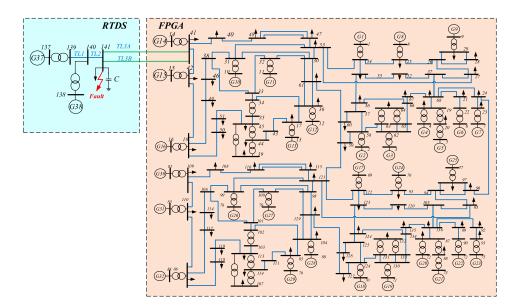

Fig. 3 shows the architecture of the proposed FPGA-RTDS co-simulator. It can be seen from the figure that it consists of three main parts: 1) FPGA boards; 2) RTDS racks and

FIGURE 3. Architecture of the proposed co-simulator.

3) user PC. The FPGA and RTDS are carrying the main computational burdens, while the user PC is used for results visualization and system manipulations.

### A. INTERFACE DESIGN

#### 1) STUDY SYSTEM & EXTERNAL SYSTEM

The study of large-scale power system can be carried out by dividing the system into two subsystems: the study system and external system. The study system is the part of system that is of research interest, where frequent modifications of controller parameters, system topologies and fault conditions are normally required. The external system is the rest part of the system external to the study system, which is normally of much larger size but requires much less modifications during simulation studies.

For the proposed FPGA-RTDS co-simulator, the study system is simulated in RTDS, taking the advantages of the RSCAD GUI for system modification. The external system is simulated in FPGA, making good use of the inherent paralleled architecture and high computational power of FPGA.

### 2) INTERFACE IMPLEMENTATION

The study system and external systems are interconnected through one or more transmission lines. In this way, the subsystems at both ends of the transmission lines are computationally decoupled, as long as the wave travelling time is equal to or longer than one simulation time-step.

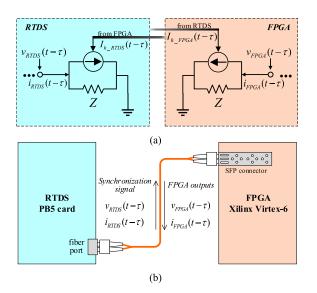

Fig. 4(a) shows the mathematical representation of the interface between FPGA and RTDS, where  $v_{RTDS}$ ,  $i_{RTDS}$ ,  $v_{FPGA}$  and  $i_{FPGA}$  are the terminal voltages and line currents at RTDS side and FPGA side respectively;  $I_{h_{_}FPGA}$  and  $I_{h_{_}RTDS}$  are the history currents;  $\tau$  is the wave travelling time. The interface transmission line is represented by two Norton equivalent circuits, one for each terminal. The history

FIGURE 4. Interface between FPGA and RTDS. (a) Mathematical representation. (b) Physical representation.

currents of the Norton equivalents depend on the voltages and line currents from both ends, i.e.,

$$I_{h\_FPGA}(t-\tau) = -\frac{1}{Z}v_{RTDS}(t-\tau) - i_{RTDS}(t-\tau)$$

(4)

$$I_{h\_RTDS}(t-\tau) = -\frac{1}{Z} v_{FPGA}(t-\tau) - i_{FPGA}(t-\tau)$$

(5)

Fig. 4(b) shows the physical representation of the interface between FPGA and RTDS for the proposed method. As can be seen from the figure, the SFP transceiver on FPGA board is connected by bi-directional optical fiber to the I/O fiber port on RTDS PB5 processor card. It is used to exchange the terminal voltages and currents between both ends. The synchronization signal from RTDS and signals from FPGA that need to be visualized are also sent through the fiber. The fiber used in the current setup is an OM1 62.5 LC-LC multimode cable with a baud rate of 2.0 Gigabaud with 10b/8b encoding. It is able to bi-directionally transfer up to 64 32-bit signals in each direction in every simulation time-step. There are up to 4 I/O fiber ports available on each PB5 card. The Aurora protocol developed by Xilinx is used for high speed point to point communication.

It is important to mention that the implementation of Norton equivalent at RTDS side does not require access to the low level codes of RTDS, as its impedance is purely resistive and no "history terms" are required. The history current and equivalent parallel impedance of Norton equivalent can be modelled using controlled current sources and resistors.

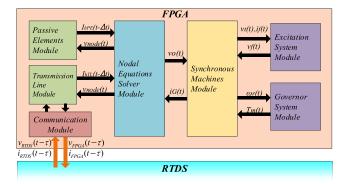

At the FPGA side, computations are synchronized with the RTDS at the start of each simulation time-step using the synchronization signal. The actual network solution, which is decoupled from that at RTDS side, is carried out once the exchange of data between the FPGA and RTDS is completed. The calculated terminal voltages and currents are sent to the communication hardware module, as shown in Fig. 5, waiting for the exchange of signals with RTDS side.

# 3) OUTPUT FROM FPGA

Detailed simulation results of the external system are computed and stored in FPGA. They can be exported in various ways. For example, data can be exported to PC through USB cable or RS232. It can also be displayed on an oscilloscope through a D/A converter. For the proposed co-simulator, FPGA output signals are exported to RTDS through the fiber connection between FPGA and PB5 card as shown in Fig. 4(b) and visualized using RSCAD. On one hand, the GUI of RSCAD can be used for better manipulation

FIGURE 5. Hardware modules for FPGA implementation.

of the output signals. On the other hand, it would be more convenient when simulation results from FPGA and RTDS can both be accessed through RSCAD.

#### **IV. HARDWARE IMPLEMENTATION**

For the hardware implementation using FPGA, the following hardware modules have been designed for most of the commonly used power system components: passive elements module, transmission line module, nodal equations solver module, synchronous machine module and the excitation system module & governor/turbine system module for synchronous machines. The interconnections between these modules are illustrated in Fig. 5. It can be seen form the figure that each module is made responsible for the calculation of one type of power system/control element to take advantage of the inherent parallelism between different hardware modules.

At the same time, deeply pipelined calculation algorithms have been designed within each module itself. So the calculations of all the elements of the same type that are sharing the same hardware module are carried out in a pipelined manner. In some cases the hardware module may need to be duplicated for one particular type of element when the number of elements is large or the computation is complex. This way of design effectively avoids the potential problem of computation delay caused by one excessively complex module.

# A. PARALLELED COMPUTATION SCHEMES IN FPGA

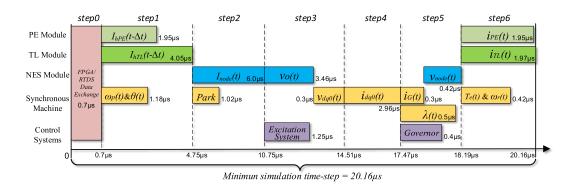

Considering the inherent parallelism between modules and the pipelined computation within each module, 7 steps of calculations are designed within each time-step as shown in Fig. 6. It can be seen that more than one hardware modules are processed in parallel in most of the steps.

Step 0: The terminal voltages and currents of the interface transmission line are exchanged between FPGA and RTDS.

Step 1: The calculation of history currents of passive elements and transmission lines and the prediction of rotor speed and angle are carried out in parallel.

Wait for ∆t over

FIGURE 6. Computation schemes of subsystem in FPGA.

$t + \Delta t$

Step 2: Nodal current injections ( $I_{node}$ ) and the park transformation matrix are calculated in parallel using the history currents and the predicted rotor angle from step 1.

Step 3: Using the nodal current injections from step 2, the equivalent system open-circuit voltage  $v_o$  for each synchronous machine and its value in dq0 reference frame, i.e.  $v_{dq0}$  are calculated. At the same time, the inverse of park transformation matrix and the excitation voltage  $v_f$  for each synchronous generator are calculated in parallel.

Step 4: This step is to calculate the stator currents in dq0 reference frame, i.e.  $i_{dq0}$  for each synchronous machine. The values of  $v_{dq0}$ ,  $v_f$ , and predicted rotor speed  $\omega_p$  from previous time-steps are required as inputs.

Step 5: The calculated  $i_{dq0}$  from step 4 is taken as input for the calculation of flux linkages ( $\lambda$ ), and stator current in *abc* reference frame ( $i_G$ ) for each synchronous machine. Then the system nodal voltages  $v_{node}$  are calculated using the calculated values of  $i_G$ .

Step 6: The currents of passive elements and transmission lines are calculated in this step. Also the rotor speed of each synchronous machine is calculated using the flux linkage and mechanical torque input from the governor system. These values will be used in step 1 of next time-step.

Upon completion of step 6, the simulator will idle until the end of current time-step before starting the next step 0.

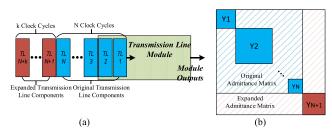

#### **B. PLATFORM EXPANDABILITY**

The proposed co-simulator has been designed so that the simulated AC system in FPGA can be conveniently expanded without significant sacrifice of hardware resources and computational efficiency. Therefore each of the hardware modules shown in Fig. 5 has been designed as a fully self-contained module with dedicated interface signals for

interconnection with other modules. In addition, the pipelined computation schemes of elements in each module greatly facilitate the system expansion.

Fig. 7 illustrates how system expansion can be carried out with the modular design. Take transmission line module as an example, Fig. 7(a) schematically illustrates how the additional components can be accommodated in the designed hardware modules. In the figure, TL1-TLN are N transmission line components that have been simulated in the original system, and suppose that additional k transmission line components need to be added. The computations of these additional transmission lines can be pipelined with the existing ones so the increase of computational time of this hardware module is k FPGA clock cycles. Due to the high clock frequency of FPGA, the corresponding increase of time is very small. Similar methods are applied to other modules. At the same time the system admittance matrix is expanded as shown in Fig. 7(b). Due to the decoupling effect of transmission lines, the expanded part of the system (with a system matrix of YN+1) can be solved independently from and in parallel with existing networks.

FIGURE 7. Hardware implementation of network expansion (a) Network expansion of transmission line components; (b) Network expansion of admittance matrix.

Another important aspect with system expansion is its effect on the minimum simulation time-step. The proposed expansion method can effectively reduce the increase of the minimum simulation time-step. If the method of pipelining to accommodate more components does not lead to longer solution time than the hardware modules that are processed in parallel, its impact on the overall simulation time-step is minimal. On the contrary, if the network expansion is significant and results in an excessive amount of one particular type of component, additional hardware modules may need to be added. A more detailed discussion on this aspect will be provided in the next section based on the case studies.

### **V. SIMULATION RESULTS**

Two case studies using the proposed co-simulator based on Xilinx Virtex-6 FPGA and RTDS are presented in this section. Case 1 is to verify the accuracy of the proposed co-simulator and case 2 is to demonstrate the simulation capability of the co-simulator. The achieved minimum simulation time-steps are 5.71  $\mu$ s for case 1 and 20.16  $\mu$ s for case 2 with 100 MHz FPGA clock frequency.

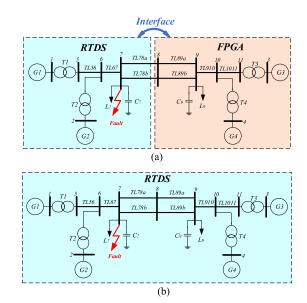

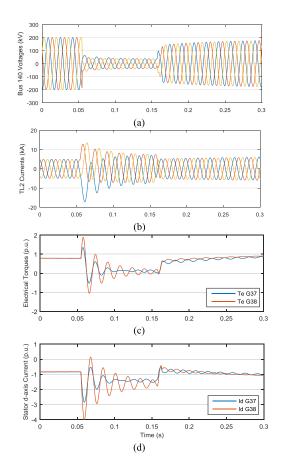

#### A. CASE 1

Fig. 8 illustrates the simulation case. It can be seen in Fig. 8(a) that the two-area four-machine system is divided into two subsystems when simulated using the proposed co-simulator. The area with G1 and G2 are simulated using RTDS, while the other area with G3 and G4 are simulated in FPGA. The two subsystems are interfaced by the transmission line *TL78*. The system parameters are obtained from [28]. The excitation and governor systems for the generators are as described in Section II. To verify the accuracy of the co-simulator, the same system is simulated in RTDS as a comparison, which is illustrated in Fig. 8(b). A 150ms three-phase fault located at bus 7 is simulated.

FIGURE 8. Simulation of two-area four-machine system. (a) Using the proposed co-simulator; (b) Using RTDS only.

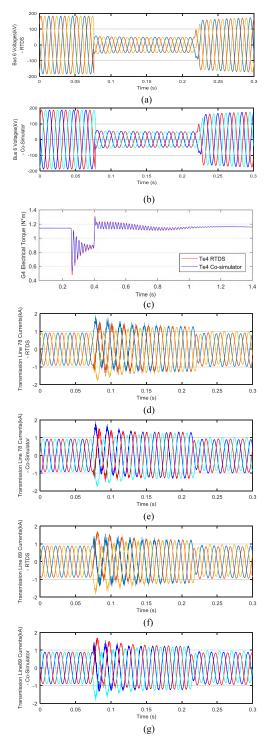

Fig. 9 shows the comparisons of simulation results. Fig. 9(a) and Fig. 9(b) compare the simulation results of three-phase voltages at bus 6 from the co-simulator and RTDS. It can be seen that once fault happens, the voltages are dropped with high-frequency oscillations. Detailed agreement can be observed. Fig. 9(c) shows the comparison of electrical torques of generator G4. It can be seen that the oscillatory behaviours are accurately simulated using the proposed method. Fig. 9(d) to Fig. 9(g) show the comparison of transmission line currents on TL78a and TL89a. It can be observed that both the transients and the unbalance between three-phases are accurately simulated using the proposed co-simulator.

The matching of simulation results between the proposed method and the RTDS is expected as the same type of component models (EMT models) are used for both the FPGA and RTDS sides. Therefore no special interface technique (required for EMT-TS hybrid simulation) needs to be designed. At the same time, the size of the network that can be simulated is not compromised which will be illustrate in case 2. In addition, to further demonstrate the simulation

**FIGURE 9.** Simulation results for case 1. (a) Bus 6 voltages from RTDS. (b) Bus 6 voltages from the co-simulator. (c) Electrical torques of G4 from RTDS and the co-simulator. (d) Three-phase line currents on *TL78a* from RTDS. (e) Three-phase line currents on *TL78a* from RTDS. (g) Three-phase line currents on *TL89a* from RTDS

potential of the proposed method, the relationships between the size of the network and the minimum simulation timestep/hardware resource are discussed in Section VI.

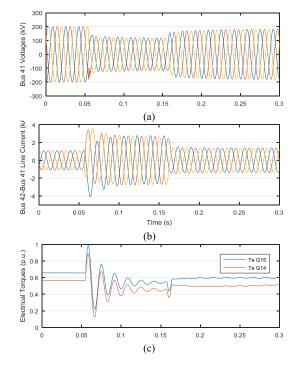

#### B. CASE 2

To demonstrate the capability of simulating large AC networks using the proposed co-simulator, a system with 141 three-phase buses are developed as shown in Fig. 10. Five buses and two machines (G37 and G38) are simulated in RTDS, and the rest of the network is simulated in FPGA. The two subsystems are interfaced by transmission lines *TL3A* and *TL3B*. The simulated fault is a 100 ms three-phase fault located at bus 141.

As a comparison, if the same system is simulated using only RTDS, 4 PB5 racks will be needed, while with the proposed method, only 1 FPGA board and half of the computational resource in 1 PB5 rack are used. Furthermore, as will be shown in Section VI, the remaining hardware resource of FPGA board is still significant. This means that even larger systems can be simulated based on the current setup without hardware expansion.

Fig. 11 and Fig. 12 show the simulation results using the proposed co-simulator. It can be seen that once fault happens at bus 141, the voltages at bus 140 at RTDS side (Fig. 11(a)) and bus 41 at FPGA side (Fig. 12(a)) are decreased. The three-phase currents on the connected transmission lines, i.e., *TL2* at RTDS side and the line between bus 42 and bus 41 at FPGA side are increased as shown in Fig. 11(b) and Fig. 12(b). The electrical torques of *G37* and *G38* at RTDS side are shown in Fig. 11(c). Higher oscillations are observed in electrical torques of *G38* as it is located electrically closer to the fault. Similar oscillatory responses of the stator *d*-axis current of *G37* and *G38* are shown in Fig. 11(d). The electrical torques of *G14* and *G15* are shown in Fig. 12(c) where smaller oscillations can be seen.

#### **VI. DISCUSSIONS**

To examine the relationship between hardware utilization and the size of AC network, Table I shows the FPGA resource utilizations for case 1 and case 2. It can be seen from the table that the utilization rate of each type of hardware resource is only increased by a factor of 3.3 - 3.7, while the size of FPGA part of the system is increased by more than 20 times. It is mainly due to the expansion method as discussed in Section IV.

To analyze how network expansion affects the minimum simulation time-step, Fig. 13 shows how the minimum simulation time-step is affected by the processing time of paralleled hardware modules. Taking Case 2 as an example, the detailed timing for each step is shown in the figure when

TABLE 1. FPGA resource utilization.

| FPGA Hardware Resource Utilization |              |               |           |

|------------------------------------|--------------|---------------|-----------|

| Logic Utilization                  | Case1        | Case2         | Available |

| Slice Registers                    | 15860(5.3%)  | 52466(17.4%)  | 301440    |

| Slice LUTs                         | 30242(20.1%) | 110283(73.2%) | 150720    |

| Block RAMs                         | 13(3.1%)     | 45(10.8%)     | 416       |

| DSP48E1s                           | 87(11.3%)    | 307(40.0%)    | 768       |

FIGURE 10. Single-line diagram of the 141-bus system.

**FIGURE 11.** Simulation results of from RTDS. (a) Three-phase voltages at bus 140. (b) Three-phase currents on *TL2*. (c) Electrical torques of *G37* and *G38*. (d) Stator *d*-axis current of *G37* and *G38*.

the FPGA clock frequency is 100 MHz. The horizontal axis represents the minimum simulation time-step of FPGA, which can be further divided into step 0-6 as discussed in Section IV. As can be seen from the figure, the processing

**FIGURE 12.** Simulation results from FPGA. (a) Three-phase voltages at bus 41. (b) Three-phase line currents between bus 42 and bus 41. (c) Electrical torques of *G14* and *G15*.

time of each step is determined by the most time-consuming hardware module in that step. For example, the processing time of step 1 is determined by the transmission line module. Therefore, the increase of calculation time to other modules in the same step does not lead to an increase of the minimum simulation time-step, as long as it is still smaller than the largest one. For example, at step 1 of case 2, the processing times of passive element module, transmission line module

FIGURE 13. Breakdown of minimum simulation time-step of Case 2.

and  $\omega_p \& \theta$  (prediction of rotor speed and angle) module are 1.95  $\mu$ s, 4.05  $\mu$ s and 1.18  $\mu$ s respectively. So an additional 4.05  $\mu$ s -1.95  $\mu$ s = 2.1 $\mu$ s of calculation time is available for the passive element module in this step. It means that theoretically up to 210 additional passive elements can be pipelined into the same hardware module without affecting the processing time of step 1 when the FPGA clock frequency is 100 MHz.

When a large numbers of synchronous generators need to be added, the processing time of all steps are affected. Additional hardware modules are needed to increase the level of parallelism to maintain the simulation time-step. However considering the achieved minimum simulation timesteps of 5.71  $\mu$ s for case 1 and 20.16  $\mu$ s for case 2, the size of network expansion that can be accommodated would be significant before the minimum simulation time-step reaches the typical RTS time-step of around 50  $\mu$ s.

#### **VII. CONCLUSION**

This paper has proposed an FPGA-RTDS co-simulator for the real-time simulation of large power systems. Under this arrangement, the FPGA provides an efficient extension to the RTDS, alleviating the limitations on the size of AC system that can be simulated with detailed EMT models. At the same time, it avoids the interface errors existing in hybrid EMT-TS simulation methods. To achieve better expandability of the co-simulator, hardware modules have been designed as fully self-contained modular components for most of the commonly used power system elements. They can be conveniently duplicated when the size of the system expands, and the effect on simulation time-step is minimized. Two case studies have been presented to verify the accuracy and capability of the proposed co-simulator. Discussions based on the case studies have been presented to further demonstrate the potential of the proposed co-simulator in simulating even larger systems with sufficiently small time-steps.

# REFERENCES

- [1] W. Hualei and M. A. Redfern, "Enhancing AC networks with HVDC interconnections," in *Proc. CICED*, Sep. 2010, pp. 1–7.

- [2] M. Liserre, T. Sauter, and J. Y. Hung, "Future energy systems: Integrating renewable energy sources into the smart power grid through industrial electronics," *IEEE Ind. Electron. Mag.*, vol. 4, no. 1, pp. 18–37, Mar. 2010.

- [3] R. Li, C. Booth, A. Dysko, A. Roscoe, H. Urdal, and J. Zhu, "Protection challenges in future converter dominated power systems: Demonstration through simulation and hardware tests," in *Proc. Int. Conf. Renew. Power Gener. (RPG)*, 2015, pp. 1–6.

- [4] H. Saad, Y. Fillion, S. Deschanvres, Y. Vernay, and S. Dennetiere, "On resonances and harmonics in HVDC-MMC station connected to AC grid," *IEEE Trans. Power Del.*, vol. 32, no. 3, pp. 1565–1573, Jun. 2017.

- [5] H. Urdal, R. Ierna, J. Zhu, C. Ivanov, A. Dahresobh, and D. Rostom, "System strength considerations in a converter dominated power system," *IET Renew. Power Gener.*, vol. 9, no. 1, pp. 10–17, 2015.

- [6] P. M. Menghal and A. J. Laxmi, "Real time simulation: Recent progress & challenges," in *Proc. Int. Conf. Power, Signals, Controls Comput.*, Jan. 2012, pp. 1–6.

- [7] M. D. O. Faruque *et al.*, "Real-time simulation technologies for power systems design, testing, and analysis," *IEEE Power Energy Technol. Syst. J.*, vol. 2, no. 2, pp. 63–73, Jun. 2015.

- [8] V. Jalili-Marandi, V. Dinavahi, K. Strunz, J. A. Martinez, and A. Ramirez, "Interfacing techniques for transient stability and electromagnetic transient programs IEEE task force on interfacing techniques for simulation tools," *IEEE Trans. Power Del.*, vol. 24, no. 4, pp. 2385–2395, Oct. 2009.

- [9] F. Tian, C. Yue, Z. Wu, and X. Zhou, "Realization of electromechanical transient and electromagnetic transient real time hybrid simulation in power system," in *Proc. IEEE/PES Transmiss. Distrib. Conf. Expo., Asia Pacific*, Aug. 2005, pp. 1–6.

- [10] X. Zhang, A. J. Flueck, and S. Abhyankar, "Implicitly coupled electromechanical and electromagnetic transient analysis using a frequencydependent network equivalent," *IEEE Trans. Power Del.*, vol. 32, no. 3, pp. 1262–1269, Jun. 2017.

- [11] D. Shu, X. Xie, Q. Jiang, Q. Huang, and C. Zhang, "A novel interfacing technique for distributed hybrid simulations combining EMT and transient stability models," *IEEE Trans. Power Del.*, vol. 33, no. 1, pp. 130–140, Feb. 2018.

- [12] F. Plumier, P. Aristidou, C. Geuzaine, and T. van Cutsem, "Co-simulation of electromagnetic transients and phasor models: A relaxation approach," *IEEE Trans. Power Del.*, vol. 31, no. 5, pp. 2360–2369, Oct. 2016.

- [13] Q. Huang and V. Vittal, "Application of electromagnetic transient-transient stability hybrid simulation to FIDVR study," *IEEE Trans. Power Syst.*, vol. 31, no. 4, pp. 2634–2646, Jul. 2016.

- [14] A. S. Morched, J. H. Ottevangers, and L. Marti, "Multi-port frequency dependent network equivalents for the EMTP," *IEEE Trans. Power Del.*, vol. 8, no. 3, pp. 1402–1412, Jul. 1993.

- [15] B. Gustavsen and A. Semlyen, "Rational approximation of frequency domain responses by vector fitting," *IEEE Trans. Power Del.*, vol. 14, no. 3, pp. 1052–1061, Jul. 1999.

- [16] B. Gustavsen and H. M. J. De Silva, "Inclusion of rational models in an electromagnetic transients program: Y-parameters, Z-parameters, S-parameters, transfer functions," *IEEE Trans. Power Del.*, vol. 28, no. 2, pp. 1164–1174, Apr. 2013.

- [17] Y. Chen and V. Dinavahi, "FPGA-based real-time EMTP," *IEEE Trans. Power Del.*, vol. 24, no. 2, pp. 892–902, Apr. 2009.

- [18] Y. Chen and V. Dinavahi, "Hardware emulation building blocks for realtime simulation of large-scale power grids," *IEEE Trans. Ind. Informat.*, vol. 10, no. 1, pp. 373–381, Feb. 2014.

- [19] Y. Chen and V. Dinavahi, "Multi-FPGA digital hardware design for detailed large-scale real-time electromagnetic transient simulation of power systems," *IET Gener., Transmiss., Distrib.*, vol. 7, no. 5, pp. 451–463, May 2013.

- [20] Z. Shen and V. Dinavahi, "Real-time device-level transient electrothermal model for modular multilevel converter on FPGA," *IEEE Trans. Power Electron.*, vol. 31, no. 9, pp. 6155–6168, Sep. 2016.

- [21] M. Dagbagi, L. Idkhajine, E. Monmasson, and I. Slama-Belkhodja, "FPGA implementation of power electronic converter real-time model," in *Proc. Int. Symp. Power Electron. Power Electron., Elect. Drives, Automat. Motion*, Jun. 2012, pp. 658–663.

- [22] F. Dijkhuizen, "Recent advances and challenges of power electronics for transmisson applications," in *Proc. 8th Int. Conf. Exhib. Ecol. Vehicles Renew. Energies (EVER)*, Mar. 2013, pp. 1–4.

- [23] E. Levi, N. Bodo, O. Dordevic, and M. Jones, "Recent advances in power electronic converter control for multiphase drive systems," in *Proc. IEEE Workshop Elect. Mach. Design, Control Diagnosis (WEMDCD)*, Mar. 2013, pp. 158–167.

- [24] H. W. Dommel, "Digital computer solution of electromagnetic transients in single- and multiphase networks," *IEEE Trans. Power App. Syst.*, vol. PAS-88, no. 4, pp. 388–399, Apr. 1969.

- [25] H. W. Dommel, "Nonlinear and time-varying elements in digital simulation of electromagnetic transients," *IEEE Trans. Power App. Syst.*, vol. PAS-90, no. 6, pp. 2561–2567, Nov. 1971.

- [26] H. K. Lauw and W. S. Meyer, "Universal machine modeling for the representation of rotating electric machinery in an electromagnetic transients program," *IEEE Trans. Power App. Syst.*, vol. PAS-101, no. 6, pp. 1342–1351, Jun. 1982.

- [27] IEEE Recommended Practice for Excitation System Models for Power System Stability Studies, IEEE Standard 421.5-2016 (Revision of IEEE Standard 421.5-2005), 2016, pp. 1–207.

- [28] P. Kundur, Power System Stability and Control. New York, NY, USA: McGraw-Hill, 1994.

**CONGHUAN YANG** received the B.Eng. degree in electrical and electronic engineering from the Huazhong University of Science and Technology, Wuhan, China, in 2013, and the Ph.D. degree in electronic and electrical engineering from the University of Birmingham, Birmingham, U.K., in 2018. Her research interests include power system EMTP simulation and HVDC.

**YING XUE** received the B.Eng. and Ph.D. degrees in electronic electrical and computer engineering from the University of Birmingham, Birmingham, U.K., in 2012 and 2016, respectively. He is currently a Lecturer of electrical power systems with the University of Birmingham. His research interests include HVDC modeling and control and power system simulation.

...

**XIAO-PING ZHANG** (M'95–SM'06) received the B.Eng., M.Sc., and Ph.D. degrees in electrical engineering from Southeast University, China, in 1988, 1990, and 1993, respectively. He was an Associate Professor with the University of Warwick, England, U.K. He was with the China State Grid EPRI (NARI Group) on EMS/DMS advanced application software research and development from 1993 to 1998. From 1998 to 1999 he was visiting UMIST. From 1999 to 2000, he was

an Alexander-von-Humboldt Research Fellow with the University of Dortmund, Germany. He is currently a Professor of electrical power systems with the University of Birmingham, U.K., and he is also the Director of the Smart Grid, Birmingham Energy Institute, and the Co-Director of the Birmingham Energy Storage Center. He has co-authored the first and second editions of the monograph *Flexible AC Transmission Systems: Modeling and Control* (Springer, 2006 and 2012). He has co-authored the book *Restructured Electric Power Systems: Analysis of Electricity Markets with Equilibrium Models* (IEEE Press/Wiley, 2010). He pioneered the concept of "Energy Quality," "Global Power and Energy Internet," "Energy Union," and "UK's Energy Valley". He is an Advisor to the IEEE PES UK and Ireland Chapter.

**YI ZHANG** (M'05–SM'11) received the Ph.D. degree in electrical engineering from Shanghai Jiao Tong University in 1998. He joined RTDS Technologies Inc. in 2000 and currently holds the position of CTO and Vice-President Research and Development. He has been a member of the RTDS Developing Team for over 18 years. He is a Registered Professional Engineer in the Province of Manitoba. He also serves as an Adjunct Professor at the University of Manitoba.