## UNIVERSITY<sup>OF</sup> BIRMINGHAM University of Birmingham Research at Birmingham

# High temperature nanoscratching of single crystal silicon under reduced oxygen condition

Chavoshi, Saeed Zare; Corujeira Gallo, Santiago; Dong, Hanshan; Luo, Xichun

DOI: 10.1016/j.msea.2016.11.097

*License:* Creative Commons: Attribution-NonCommercial-NoDerivs (CC BY-NC-ND)

Document Version Peer reviewed version

#### Citation for published version (Harvard):

Chavoshi, ŚZ, Corujeira Gallo, S, Dong, H & Luo, X 2017, 'High temperature nanoscratching of single crystal silicon under reduced oxygen condition', *Materials Science and Engineering A*, vol. 684, pp. 385-393. https://doi.org/10.1016/j.msea.2016.11.097

Link to publication on Research at Birmingham portal

#### **General rights**

Unless a licence is specified above, all rights (including copyright and moral rights) in this document are retained by the authors and/or the copyright holders. The express permission of the copyright holder must be obtained for any use of this material other than for purposes permitted by law.

•Users may freely distribute the URL that is used to identify this publication.

•Users may download and/or print one copy of the publication from the University of Birmingham research portal for the purpose of private study or non-commercial research.

•User may use extracts from the document in line with the concept of 'fair dealing' under the Copyright, Designs and Patents Act 1988 (?) •Users may not further distribute the material nor use it for the purposes of commercial gain.

Where a licence is displayed above, please note the terms and conditions of the licence govern your use of this document.

When citing, please reference the published version.

#### Take down policy

While the University of Birmingham exercises care and attention in making items available there are rare occasions when an item has been uploaded in error or has been deemed to be commercially or otherwise sensitive.

If you believe that this is the case for this document, please contact UBIRA@lists.bham.ac.uk providing details and we will remove access to the work immediately and investigate.

### Author's Accepted Manuscript

High temperature nanoscratching of single crystal silicon under reduced oxygen condition

Saeed Zare Chavoshi, Santiago Corujeira Gallo, Hanshan Dong, Xichun Luo

PII:

S0921-5093(16)31472-1

DOI:

http://dx.doi.org/10.1016/j.msea.2016.11.097

Reference:

MSA34423

To appear in: Materials Science & Engineering A

Received date: 5 August 2016 Revised date: 12 October 2016 Accepted date: 28 November 2016

Cite this article as: Saeed Zare Chavoshi, Santiago Corujeira Gallo, Hansha Dong and Xichun Luo, High temperature nanoscratching of single crystal silico under reduced oxygen condition, *Materials Science & Engineering A* http://dx.doi.org/10.1016/j.msea.2016.11.097

This is a PDF file of an unedited manuscript that has been accepted fo publication. As a service to our customers we are providing this early version o the manuscript. The manuscript will undergo copyediting, typesetting, and review of the resulting galley proof before it is published in its final citable form. Please note that during the production process errors may be discovered which could affect the content, and all legal disclaimers that apply to the journal pertain

### High temperature nanoscratching of single crystal silicon under

### reduced oxygen condition

Saeed Zare Chavoshi<sup>1</sup>, Santiago Corujeira Gallo<sup>2</sup>, Hanshan Dong<sup>2</sup>, Xichun Luo<sup>3</sup> <sup>1</sup>Department of Mechanical Engineering, Imperial College London, Exhibition Road, London, SW7 2AZ, UK

<sup>2</sup>School of Metallurgy and Materials, University of Birmingham, Edgbaston, Birmingham, B15 2TT, UK

<sup>3</sup>Centre for Precision Manufacturing, Department of Design, Manufacture and Engineering

Management, University of Strathclyde, Glasgow, G1 1XJ, UK

s.zare@imperial.ac.uk

xichun.luo@strath.ac.uk

### Abstract

cill

In-situ high temperature nanoscratching of Si(110) wafer under reduced oxygen condition was carried out for the first time using a Berkovich tip with a ramp load at low and high scratching speeds. Ex-situ Raman spectroscopy and AFM analysis were performed to characterize high pressure phase transformation, nanoscratch topography and nanoscratch hardness. No remnants of high pressure silicon phases were observed along all the nanoscratch residual tracks in high temperature nanoscratching, whereas in room temperature nanoscratching, phase transformation showed a significant dependence on the applied load and scratching speed i.e. the deformed volume inside the nanoscratch made at room temperature was comprised of Si-I, Si-XII and Si-III above different threshold loads at low and high scratching speeds. Further analysis through AFM measurements demonstrated that the scratch hardness and residual scratch morphologies i.e. scratch depth, scratch width and total pile-up heights are greatly affected by the wafer temperature and scratching speed.

### **ACCEPTED MANUSCRIPT**

Keywords: High temperature; Nanoscratching; Single crystal silicon; Polymorphs

### 1. Introduction

Silicon is a technologically crucial material and is the workhorse of the semiconductor industry due to its excellent stability, wear resistance and abundance. However, bulk wafers of single crystal silicon exhibit poor machinability at room temperature owing to their relatively low fracture toughness and high nanoindentation hardness. It is a common belief that the yield strength and hardness of silicon would reduce at high temperature. As such, the fracture toughness of silicon improves and its hardness decreases which would ease the plastic deformation and improve the machinability [1, 2].

Molecular dynamics (MD) simulation studies have been conducted on high temperature nanometric cutting of silicon for the sake of making important contributions to our fundamental understanding of the occurring processes at the atomic scale at elevated temperatures [1, 3-5]. It has been revealed that MD simulation is a robust numerical analysis tool in addressing a range of complex nanometric cutting problems that are otherwise difficult or impossible to understand using other methods. For example, the mechanics of high temperature nanometric cutting of silicon is influenced by a number of variables such as machine tool performance, cutting conditions, material properties, and cutting tool performance (material microstructure and physical geometry of the contact) and all these variables cannot be monitored online through experimental examination. However, these could suitably be studied using an advanced simulation based approach such as MD simulation. Although MD simulation offers a unique opportunity to explore the atomic level discrete processes of nanometric cutting/scratching of silicon under desired conditions, there exists some other phenomena which are impossible to be investigated using MD simulation, attributable to either the lack of a proper interatomic potential function or the excessive intricacy of the phenomenon. For instance, the available potential functions are not robust in describing and capturing all the structural phases of silicon; hence phase transformation mechanisms during nanometric cutting/scratching at room and elevated temperatures cannot be understood through MD simulation. Furthermore, the MD simulated depth of cut is only several nanometres, which is much smaller than the actual depth of cut (~ several hundred nanometres to tens of micrometres). Consequently, high pressure phase transformation cannot be simulated under such condition. Therefore, experimental determination of the formation of polymorphs is required. It should be noted here that the material removal mechanism in scratching is similar to that in cutting/machining. Hence, it is possible to substitute the complicated cutting/machining with a relatively simple scratching so as to study material removal mechanism involved in cutting/machining [6].

In this paper, the focus will be on the experimental studies of the pressure-induced silicon polymorphs, nanoscratch topography and nanoscratch hardness in nanoscratching of silicon at room and elevated temperatures. To this end, using the state-of-the-art nanoindentation equipment, in-situ high temperature nanoscratching trials on single crystal silicon wafer under inert gas are performed and ex-situ characterization techniques, such as Raman spectroscopy and atomic force microscopy (AFM) are employed to shed some light on the aforementioned processes.

#### 2. Literature review

The previous work on nanoscale cutting/scratching/indentation by MD simulation has primarily focused on demystifying the material removal mechanisms at "room temperature". What is known from these studies is that the current pool of knowledge on the nanometric cutting/scratching/indentation at elevated temperatures is still sparse. Only limited work has been done so far on studying hot nanoscale cutting/scratching/indentation by MD. In preliminary investigations performed by the authors, hot nanometric cutting of single crystal silicon and silicon carbide on different crystal orientations was compared with the cutting at room temperature (27°C) so as to characterize the cutting mechanics such as material flow, stagnation region, specific cutting energy, cleavage and defect-mediated plasticity [1, 3-5, 7-9]. Fang et al. [10] and Liu et al. [11] performed MD simulations to examine the variation in Young's modulus, hardness and elastic recovery of copper, diamond and gold during nanoindentation at high temperatures (up to 327°C). They concluded that Young's modulus, hardness and the extent of elastic recovery decreases with the increase of temperature. Hsieh et al. [12] used MD simulation to investigate the effect of temperature on maximal normal forces and elastic recovery during nanoindentation of copper. They reported a reduction in the aforementioned parameters with an increase in the substrate temperature.

On the experimental side, there is no study hitherto on high temperature nanometric cutting/scratching. However, there is a history of using 'hot hardness'

4

microindentation tests, beginning with Atkins and Tabor [13]. Nevertheless, instrumented hardness tests at high temperatures have a shorter history. Wheeler and co-workers [14-16] have described the general nano-mechanical test platform capable of performing variable temperature and variable strain rate testing. The thermal management and measurement techniques and vacuum nanoindentation have been discussed in their review papers. Similarly, Schuh and his colleagues [17, 18] produced an elegant discussion of the technical issues surrounding high temperature nanoindentation in ambient and inert environments.

In 1996, Suzuki and Ohmura [19] performed ultra-microindentations on {110} surfaces of single crystal silicon in the temperature range of 20-600°C and concluded that below 500°C, the temperature-insensitive hardness is determined by the transformation to the metallic  $\beta$ -tin phase, which amorphizes or nanocrystallizes during unloading, while above 500°C, plastic deformation due to dislocation activity causes temperature-dependent hardness. Smith and Zheng [20] modified a depth sensing indentation instrument to measure small scale hardness and elastic modulus of glass, gold, and single crystal silicon at 200°C. The hardness and elastic modulus of soda lime glass and gold were found to be lower than that at room temperature. In contrast, indentation testing of Si(100) at  $200^{\circ}$ C produced a similar hardness value to that obtained at room temperature, although the modulus was reduced, from 140.3 to 66 GPa. In addition, the well-known 'pop out' event, which is observed during unloading of a silicon indentation at room temperature, disappeared at 200°C. Beake and Smith [21] demonstrated that mechanical properties of fused silica exhibit a completely different temperature dependence from those of soda-lime glass during high temperature nanoindenation at 400°C, since fused silica is an anomalous glass. Xia et al. [22] observed that the surface hardness of Fe-40Al, an iron aluminide, is higher and the elastic modulus is lower at elevated temperatures (400°C) than the corresponding values at room temperature. Lund et al. [23] investigated the effect of temperature during nanoindentation of pure platinum. They reported that the transition from elastic to plastic deformation takes place at progressively lower stress levels as temperature is increased. By adapting a commercial nanoindenter to allow testing at up to 200°C, Schuh *et al.* [24] explored the deformation map of two type of metallic glasses, and found that increasing the temperature at a constant indentation rate sees the gradual emergence of homogeneous flow, as thermal relaxations allow dissipation of strain localization into general viscous flow. Nanoindentation studies of single crystal Ni-base superalloy CMSX-4 oriented in the  $\langle 001 \rangle$  and  $\langle 110 \rangle$ directions were conducted by Sawant and Tin [25] over a range of temperatures from 30°C to 400°C. Trelewicz and Schuh [26] carried out high-temperature nanoindentation experiments to assess the activation enthalpy for deformation of nanocrystalline Ni-W alloys, for grain sizes between 3 and 80 nm. They reported that thermal softening becomes less pronounced at finer grain sizes, and the activation enthalpy has an apparent inflection at a grain size near  $\sim 10-20$  nm, in the vicinity of the Hall-Petch breakdown. It should be noted here that large amount of studies have been performed on the high temperature nanoindentation of various materials [27-36]. However, for the sake of brevity, only studies on silicon are discussed in the following paragraphs. Bradby and his co-workers [37, 38] reported that in hot nanoindentation of silicon, increasing temperature enhances the nucleation of Si-III and Si-XII during unloading but the final composition of the phase transformed zone is also dependent on the thermal stability of the phases in their respective matrices.

Besides, they found that the region under the indenter undergoes rapid volume expansion at temperatures above 125°C during unloading. Moreover, polycrystalline Si-I was the predominant end phase for indentation in crystalline silicon whereas high-pressure Si-III/Si-XII phases were the result of indentation in amorphous silicon. They also concluded that the Si-II phase is unstable in a c-Si matrix at elevated temperatures. In a similar work, Domnich et al. [39] carried out hightemperature nanoindentation using Berkovich probe and observed that up to a certain critical temperature (350°C), the nanoindentation hardness of silicon is dictated by the pressure required to transform the semiconducting Si-I phase into the metallic Si-II phase of silicon. However, no phase transformation was observed above 350°C and it was suggested that the nanoindentation hardness in silicon above 350°C is dictated by dislocation glide. From what was discussed above, it can be inferred that although some studies have been performed so as to improve our understanding of high temperature nanoindentation behaviour, no methodical work is available to date on the area of high temperature nanometric cutting/scratching of silicon. It might be argued that both techniques are beneficial in understanding and characterizing the materials; nevertheless, nanometric cutting/scratching unlike nanoindentation is dominated by deviatoric stresses carrying pronounced component of shear. Consequently, the stress distribution in nanometric cutting/scratching is considerably different from that of nanoindentation; hence the results are not transferable. Accordingly, it is suggested that there is a strong need to understand the high temperature nanometric cutting/scratching mechanisms of hard-brittle materials such as silicon.

### 3. Experimental setup and test procedure USCRIPT

### 3.1. Equipment

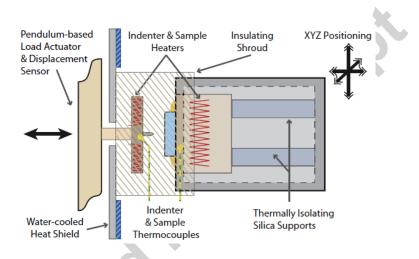

Nanoscratching trials were performed on a MicroMaterials Ltd. (MML) nanoindenter called NanoTest Vantage. This equipment permits testing at elevated temperatures with low thermal drifts under reduced oxygen/purged condition and controlled humidity levels, which offers the perfect capability for testing materials in extreme conditions. Figure 1 demonstrates the heating arrangement in the MML NanoTest Vantage system.

Figure 1: Schematics of the heating arrangement of NanoTest Vantage [14]

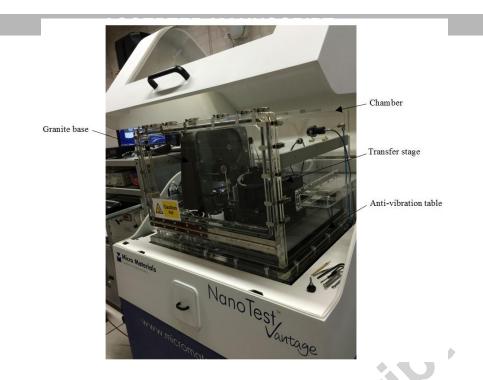

It is known that silicon is reactive with oxygen at high temperatures; hence performing nanoscratching trials under reduced oxygen condition is indispensable. NanoTest Vantage system uniquely features a chamber which can be overpressurized with a shield gas i.e. high purity Argon to surround the hot zone during testing. Figure 2 shows the configuration of NanoTest Vantage system employed for conducting the nanoscratching tests.

Figure 2: NanoTest Vantage equipment used to perform nanoscratching trials

### 3.2. Wafers and nanoindenters

The polished undoped n-type single crystal silicon wafers with the orientation (110) of size  $10 \times 10 \times 0.5$  mm were utilized for the experiments. As pointed out recently by Gerbig *et al.* [40], the augmented deviatoric stress, especially the shear stress, for the Si(110) surface as compared with the Si(100) and Si(111) surfaces could ease the plastic deformation processes leading to decreased transformation pressures in silicon. Moreover, there is little work on the material removal mechanisms of the Si(110) surface in nanoscratch testing [41].

Prior to trials, the silicon wafers were first ultrasonically cleaned for 20 min in acetone, then dipped into 2% HF (Hydrofluoric) aqueous solution for 60 min to remove the oxide layers, followed by a thorough rinse in de-ionized water. The surface roughness of the etched wafers was measured in four areas using a white light interferometer (Zygo CP300). The etched wafers had an average flatness of

Berkovich nanoindenter with a nominal tip radius of  $\geq 50$  nm and having 3-sided pyramidal faces forming an angle of 65.03° with the vertical axis was employed in the nanoscratching experiments reported here. The Berkovich nanoindenter would provide the more pragmatic conditions which could be confronted in actual applications. In addition, the use of this type of nanoindenter would lead to the much higher local pressure with similar load thus would be beneficial in elucidating the pressure-induced phase transformation problems.

### **3.3. Experimental procedure**

Nanoscratching experiments were carried out at substrate temperatures of 25°C and 500°C using a linearly increasing load spanning from 0 to 10 mN along a total scratch length of 100  $\mu$ m at two constant speeds of 0.1  $\mu$ m/s (low speed) and 10  $\mu$ m/s (high speed). At each scratching speed, three scratches were produced. The nanoscratches were made along the Si<100> direction. Nanoscratching trials at room temperature (25°C) were conducted under atmospheric conditions whereas hot nanoscratching experiments were performed under reduced oxygen condition through an overpressure of pure Argon in the chamber. The amount of oxygen in the chamber was kept in the range of ~0.2-0.3% during the experiments. The experimental parameters and conditions used for the trials are summarized in Table 1.

Table 1: Nanoscratching conditions

| Silicon | Scratching | Temperature | Scratching  | Ramp | Total   | Inert gas for |

|---------|------------|-------------|-------------|------|---------|---------------|

| wafer   | direction  | (°C)        | speed       | load | scratch | high          |

|         |            |             | $(\mu m/s)$ | (mN) | length  | temperature   |

|         |            |             |             |      | (µm)    | testing       |

| Si      | Si <100>   | 25 and 500  | 0.1 and 10  | 0-10 | 100     | Argon         |

| (110)   |            |             |             |      |         |               |

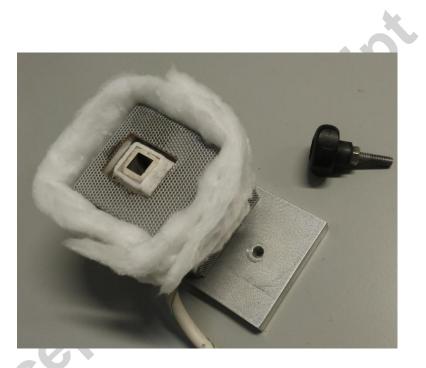

For the room temperature experiments, the wafer was glued with Cyanoacrylate onto a stainless steel disc and then fixed on the metal holder of the nanoindenter machine. For the high temperature nanoscratch testing, the wafer was glued onto the hot stage using high temperature cement, as shown in Figure 3.

Figure 3: Glued silicon wafer on the hot stage

To perform high temperature nanoscratching experiments, the wafer was heated at a low rate of 1.6°C/min to reach the target temperature. It should be mentioned that the nanoindenter was not independently heated. The swift heat transfer and thermal gradients between the heated wafer and the cold nanoindenter tip could lead to a

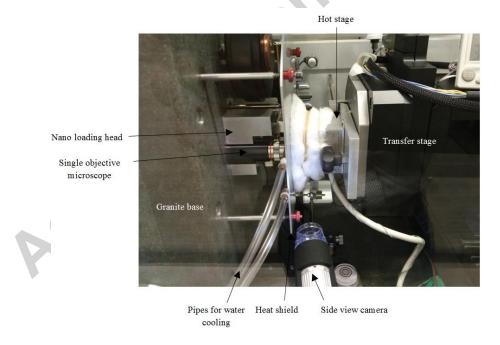

substantial thermal drift, which influences the reliability of the results. In order to minimize the thermal drift, the wafer-tip contact was achieved and wafer-tip was kept in contact during the heating process. Note that after performing high temperature nanoscratching, the wafer was cooled in the chamber at the same rate (1.6°C/min) until the room temperature was reached. Figure 4 illustrates a close snapshot of experimental system during high temperature nanoscratching. The nanoindenter and glued wafer on the hot stage were surrounded by mineral wool in order to reduce heat loss by convection and to stabilize the temperature.

After nanoscratching trials at room and high temperatures, a Thermo Scientific DXR Raman Microscope with a 532 nm diode-pumped solid state laser was used to detect the presence of crystalline and high pressure phases inside the scratches. Also, a Veeco Dimension 3100 atomic force microscope (AFM) with silicon tip was utilized to determine the topography of the nanoscratches.

Figure 4: A close snapshot of experimental system during high temperature nanoscratching

### 4. Experimental observations and discussion CRIPT

#### 4.1. Scratch topography

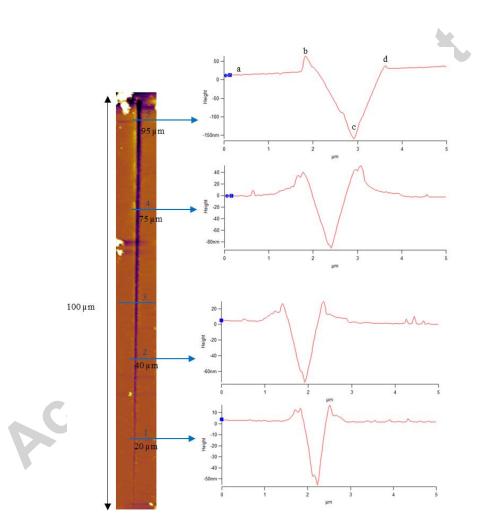

Figure 5 shows the typical topography of the residual nanoscratch measured by using the tapping mode AFM at four different positions. The cross profile topography shows a permanent pile-up (vertical height from a-b and a-d illustrated in Figure 5) at the both edges of track, which is closely associated to the plastic extrusion of silicon during nanoscratching. The heights of pile-ups are found to be asymmetric, plausibly due to the indenter tilt [42].

Figure 5: Typical AFM image of the nanoscratch and cross section profiles measured at four different positions. Scratch depth (vertical height from a-c), scratch width

(horizontal width b-d) and pile-ups (vertical height from a-b and a-d) are shown on the top profile.

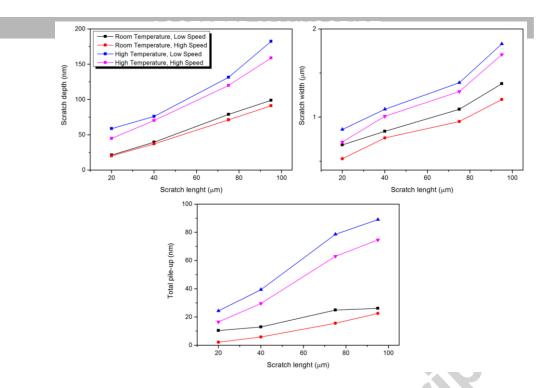

Figure 6 illustrates the variation of scratch depth, scratch width and total pile-up heights at four various positions of the nanoscratch shown in Figure 5 during nanoscratching at room and high temperatures and at two scratching speeds i.e. low speed (0.1  $\mu$ m/s) and high speed (10  $\mu$ m/s). It can be seen that with the increase of applied load and consequently pushing more material to the side of the scratches, the residual scratch depth, scratch width and total pile-up heights increase along the scratch length. Furthermore, the aforementioned parameters increase with the rise of temperature as a result of thermal softening. It is also found that the residual scratch morphologies are strongly affected by the scratching speed i.e. scratch depth, scratch width and total pile-up heights decrease with the increase of scratching speed. It can be inferred that the degree of nanoscale elastic recovery during nanoscratching is more serious at high speeds than at low speeds. The obtained results are in accord with the trend reported by Li *et al.* [43], where the residual scratch depth of K9 glass decreased with the increase of the scratching speed at the same normal load.

Accel

Figure 6: Variation of scratch depth, scratch width and total pile-up heights along the scratch length with the temperature and scratching speed

Nanoscratch hardness (H) can be employed so as to ascertain the resistance of material to the scratch, and it is described as the response of material under dynamic deformation of the surface. This parameter is defined as the ratio of the vertical load (P) to the surface area of the tip-sample contact or the contact area projection onto the horizontal plane which depends on the residual scratch width (b):

$$H = k \frac{p}{b^2} \tag{1}$$

where k is the nanoindenter tip shape factor, which is dependent on the tip configuration. For a Berkovich indenter, this factor is 2.31 [44]. The average values of scratch hardness obtained from the trials are listed in Table 2. Due to an effective reduction in the shear stress at high temperatures, the scratch hardness has lower magnitudes at high temperatures. Moreover, the scratch hardness increases as the scratching speed increases, signifying a strain rate strengthening of the silicon material at higher scratching speed. In scratch hardness, the effective strain rate can be defined as the ratio of the scratching speed to the scratch width. The strain rate hardening effect means that the material provides a greater resistance to plastic deformation [45].

| Nanoscratching condition     | Scratch hardness (GPa) |  |  |

|------------------------------|------------------------|--|--|

| Room temperature, Low speed  | 12.2                   |  |  |

| Room temperature, High speed | 16.7                   |  |  |

| High temperature, Low speed  | 7.4                    |  |  |

| High temperature, High speed | 9                      |  |  |

Table 2: Scratch hardness at different conditions

### 4.2. Nanoscratching-induced phase transformation

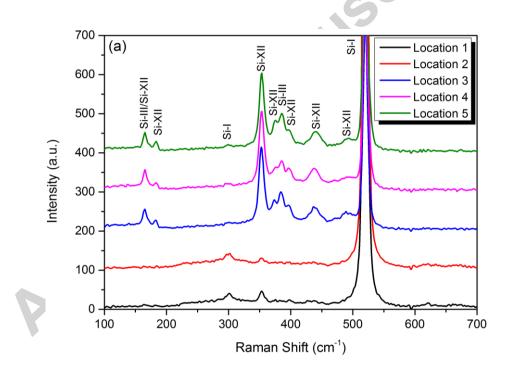

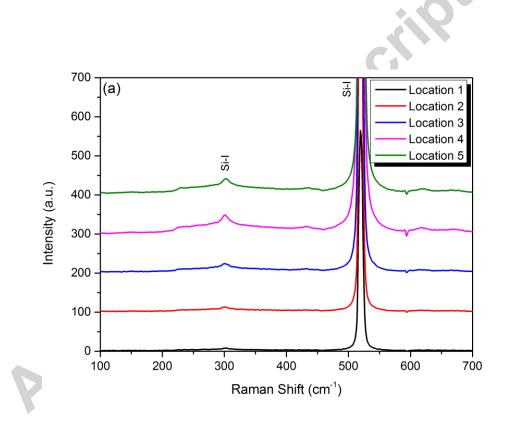

In order to identify the existence of high pressure phases of silicon inside the nanoscratch tracks, Raman spectroscopy was employed. For each scratch, the Raman spectra were collected at five different locations i.e. at the position of blue lines shown in Figure 5. It should be mentioned here that the reported phases in this study are the stable or remnant phases since the residual nanoscratch impressions were measured at room temperature after the nanoscratching experiments. Figure 7 and Figure 8 illustrate the Raman spectra of silicon obtained from the five various locations of the scratch made at room and high temperatures, respectively, at low  $(0.1 \ \mu m/s)$  and high  $(10 \ \mu m/s)$  scratching speeds. On all spectra, the single line at 519.4 cm<sup>-1</sup> can be observed, which is close to the reported 520 cm<sup>-1</sup> optical mode of bulk silicon (Si-I). Note that a small amount of stress may cause a shift. It can be

inferred from Figure 7a that while room stemperature nanoscratching at low scratching speed, the nanoscratch is composed of Si-I (bands at 520 and 300 cm<sup>-1</sup>) and high pressure phase Si-XII (band at 352 cm<sup>-1</sup>) when the scratching load is lower than ~4 mN, corresponding to the locations 1 and 2 in Figure 5. However, the intensity of the peak corresponding to Si-XII is very low, signifying that the content of Si-XII is relatively small. Above the transition load of ~5 mN, the nanoscratch is formed of Si-I, Si-XII characterized by bands at 166, 182, 352, 374, 396, 440, and 491 cm<sup>-1</sup>, and Si-III (bc8, body-centred cubic structure) identified by bands at 166 and 385 cm<sup>-1</sup>. Both Si-III and Si-XII (r8, the rhombohedral distortion of bc8) are known to show semi-metallic electronic behaviours. It is of note that the band at 385 cm<sup>-1</sup> predicted by Plitz *et al.* [46] for the bc8 structure, was attributed by Ge *et al.* [47] to Si-III together with other bands at 415 and 465 cm<sup>-1</sup>. Nevertheless, the absence of these last bands would indicate that Si-III is in minor quantity in the nanoscratch track. This observation is in good agreement with the decompression path proposed by Gassilloud et al. [48]. It is informative to note that there are strong indications that the presence of metastable crystalline phases (Si-XII and Si-III) in the residual imprints can be a consequence of formation of  $\beta$ -tin silicon (Si-II) during contact loading of silicon [49]. In other words, metallic Si-II is formed during nanoscratching owing to the highly localized stresses underneath the indenter and subsequently is transformed to Si-III and Si-XII, accompanied by >10% volume increase [6], which contributes to the elastic recovery of the scratched surface.

Interestingly, above the transition load of ~5 mN, the probability of forming Si-III and Si-XII phases was found to increase. However, the intensities remain almost

constant for these phases, suggesting that the volume of Si-III and Si-XII phases does not change at scratch loads higher than ~5 mN.

The literature suggests that the mode of unloading/release of the pressure plays a crucial rule in reverse transformation from metallic phase to crystalline phases i.e. upon slow unloading, a crystalline phase of Si-XII and Si-III may persist whereas Si-IX, amorphous silicon and Si-I could be obtained upon fast unloading. The Raman spectra shown in Figure 7b demonstrate that the nanoscratch made at high scratching speed is composed of Si-I when the scratch load is below ~7.5 mN. At higher loads i. e. ~9.5 mN, some small remnants of Si-XII and Si-III can be observed inside the scratch. As mentioned above, the high scratching speed corresponds to a high unloading rate, which likely leads to the formation of the Si-I.

Figure 7: Raman spectra collected from five different locations of the nanoscratch shown in Figure 5, and fabricated under room temperature condition at constant scratching speed of: a)  $0.1 \mu m/s$  (low speed) and b)  $10 \mu m/s$  (high speed)

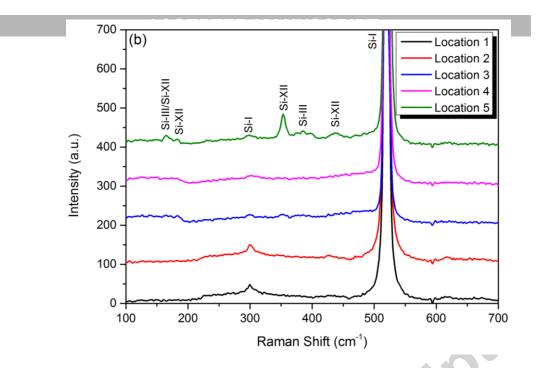

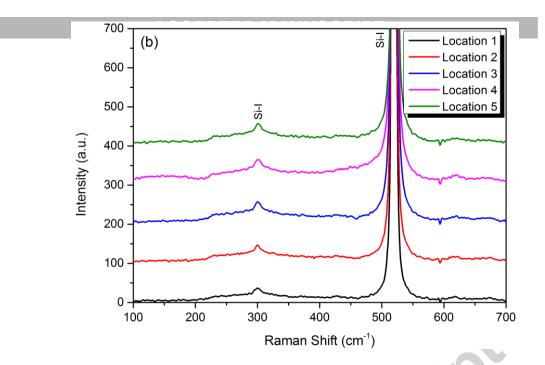

As evident in Figure 8a and Figure 8b, the Raman peaks for the Si-III and Si-XII phases disappear and no remnants of polymorph phases are detected all along the nanoscratch residual track when high temperature nanoscratching is performed at low and high speeds. This means the Si-III/XII  $\rightarrow$  Si-I phase transition occurs during the nanoscratching at high temperature of 500°C. This observation agrees with the idea that high temperature promotes the transition of metastable silicon phases (Si-III and Si-XII) into thermodynamic stable Si-I [39]. In nanoindentation process of silicon, Domnich *et al.* [39] observed that when the temperature was above 300-350°C, only cubic diamond silicon was detected, which is in excellent agreement with the obtained results of high temperature nanoscratching in our study. Moreover, there is some evidence that Si-III and Si-XII transform back to Si-I with annealing. Ruffle *et al.* [50] reported that the intensity of the peaks related to the Si-III and Si-

XII phases drops with increasing annealing time at 175°C, and after 120 min, none of these phases are detected and the Raman spectrum is similar to that of pristine silicon. Moreover, they claimed that the lifetime of the Si-III/XII is temperature dependent, and it is over 1 min at 320°C and at ambient pressure. Taking into account the high temperature nanoscratching at 500°C performed in this study, it can be assumed that annealing at 500°C with the cooling rate of 1.6 °C/min can commence a fast Si-III/XII  $\rightarrow$  Si-I phase transition during the trials. Hence, the only stable phase which is detectable from the Raman spectra shown in Figure 8 is the pristine silicon (Si-I). The obtained results in this study are also consistent with the high power laser irradiation of the indentations carried out by Zeng *et al.* [51], where rapid Si-III/XII  $\rightarrow$  Si-I phase transition within 1s was realized.

It should be noted here that other metastable phases like hexagonal diamond (Si-IV), which is characterized by a broad band at 510 cm<sup>-1</sup>, or amorphous silicon (a-Si), which is characterized by broad bands at near 170 and 490 cm<sup>-1</sup>, were not observed within the residual scratches while nanoscratching of silicon at room temperature and high temperature of 500°C using the adopted ramp load ranging from 0 to 10 mN at two constant speeds of 0.1  $\mu$ m/s (low speed) and 10  $\mu$ m/s (high speed). A possible hypothesis is that the adequate pressure for amorphization of silicon is not attained inside the scratch tracks. It can be also postulated that a-Si crystallizes during high temperature nanoscratching trials since very small volumes of a-Si typically do not require annealing temperatures exceeding 550°C in order to exhibit significant crystallization [52]. Meanwhile, there is some evidence that nanoclusters of a-Si can crystallize at temperatures as low as 70°C [53, 54]. Therefore, it is not surprising to observe the absence of a-Si within the scratch tracks. However, there might exist a

small amount of residual a-Si within the phase transformed zone, yet its amount (if present) should be very limited which cannot be detected since Raman spectroscopy itself is not very sensitive and trace amounts may not be detectable with this technique. This may be resolved by using more advanced Raman techniques such as surface-enhanced Raman scattering (SERS) and tip-enhanced Raman scattering (TERS) etc. It can be argued that cross-sectional transmission electron microscopy (XTEM) analysis can be employed to further investigate the presence of a-Si in the scratch. However, the focused ion beam (FIB) can damage the cross-sectional sample which in turn could generate a-Si within the scratch.

Figure 8: Raman spectra collected from five different locations of the nanoscratch shown in Figure 5, and fabricated under high temperature condition (500°C) at constant scratching speed of: a)  $0.1 \mu m/s$  (low speed) and b)  $10 \mu m/s$  (high speed)

### 4. Summary

Single crystal silicon nanoscratching experiments were performed at room and high temperatures to comprehend the influence of substrate temperature on the high pressure phase transformation, nanoscratch topography, nanoscratch hardness and condition of the tool tip in nanoscratching. The Raman spectroscopy results revealed that while room temperature nanoscratching at low scratching speed, above the transition load of ~5 mN, the nanoscratch is formed of Si-I, Si-XII and Si-III, and the probability of forming high pressure phases of Si-III and Si-XII increases above this load. Nevertheless, Si-III phase was found to be in minor quantity in the nanoscratch

track. At high scratching speed, small remnants of Si-XII and Si-III phases were detected when the scratch load was greater than a threshold value i. e. ~9.5 mN. When high temperature nanoscratching was carried out at low and high speeds, no remnants of polymorph phases were observed all along the nanoscratch residual track, suggesting the transition of metastable silicon phases (Si-III and Si-XII) into thermodynamic stable Si-I.

AFM measurements revealed that the residual scratch morphologies are profoundly influenced by the scratching speed viz. scratch depth, scratch width and total pile-up heights decrease with the increase of scratching speed. Moreover, the aforementioned parameters were observed to increase with the rise of temperature as a result of thermal softening. Further analysis through calculating the nanoscratch hardness showed a reduction at high temperatures. Additionally, the nanoscratch hardness was found to increase as the scratching speed increases, signifying a strain rate strengthening of silicon material at higher scratch speeds.

### Acknowledgments

The first author (SZC) would like to thank the Surface Engineering Lab at the University of Birmingham for providing equipment, support and assistance for the experimental trials. The authors also gratefully acknowledge the financial support from the EPSRC (EP/K018345/1), EPSRC (EP/L017725/1) and Royal Society-NSFC international exchange programme (IE141422) for this study.

### Appendix

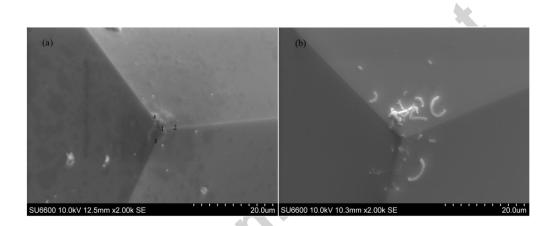

The wear mechanism of a diamond nanoindenter is very complex, involving chemical, physical, electrical, and mechanical interactions between diamond and substrate [55]. Figure A shows the scanning electron microscopy (SEM) micrograph of the nanoindenter tip taken by a Hitachi SU-6600 field emission scanning electron microscope (FE-SEM) after nanoscratching of silicon at room and high temperatures. As can be seen from the figure, under the present scratching conditions, the nanoindenter tip is not blunted i.e. mechanical wear does not occur for both cases owing to high surface hardness and wear resistance of diamond.

Figure A: SEM image of Berkovich nanoindenter tip used for nanoscratching at: a) room temperature and b) high temperature (500°C). The nanoindenter tips are not blunted under the present scratching conditions. The numbers "1, 2, 3, 4" in Figure Aa show the four locations used to collect Raman spectra.

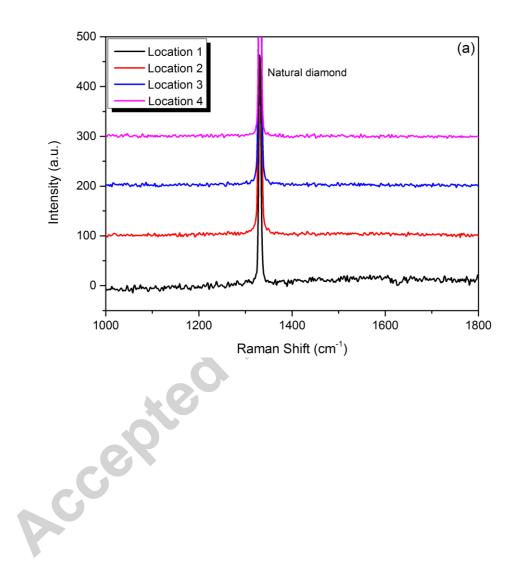

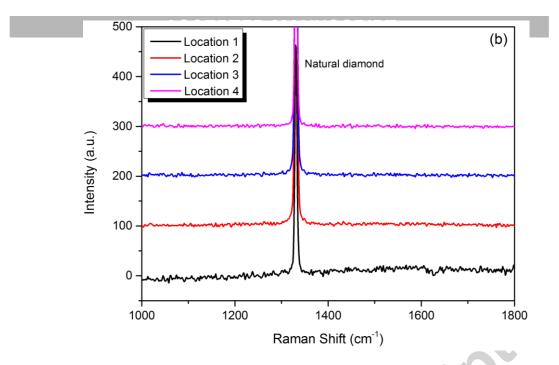

In order to study the probable microstructural changes of the diamond nanoindenter tip, Raman spectroscopy was performed at four different points on the nanoindenter edges shown in Figure Aa. Figure B illustrates the Raman spectra of the diamond obtained from the four locations of the nanoindenter tip used for nanoscratching at room and high temperatures. The strong sharp peak at 1332 cm<sup>-1</sup> corresponds to the first-order Raman peak of crystalline diamond [56]. Disordered graphite displays two

distinct modes in the Raman spectrum: the G band centred at ~1580 cm<sup>-1</sup> and the D band centred at ~1350 cm<sup>-1</sup> [57]. However, such peaks were not observed in Figure B, suggesting that under the present nanoscratching conditions, no direct diamond to graphite transformation occurred. Hence, the diamond nanoindenter is not supposed to be worn by graphitization.

Figure B: Raman spectra collected from four different locations of the nanoindenter shown in Figure Aa, used for nanoscratching at a) room temperature and b) high temperature (500°C).

### ACCEPTED References RIPT

- 1. Chavoshi, S.Z., S. Goel, and X. Luo, *Influence of temperature on the anisotropic cutting behaviour of single crystal silicon: A molecular dynamics simulation investigation.* Journal of Manufacturing Processes, 2016. **23**: p. 201-210.

- 2. Chavoshi, S.Z. and X. Luo, *Hybrid micro-machining processes: a review*. Precision Engineering, 2015. **41**: p. 1-23.

- 3. Chavoshi, S.Z., S. Goel, and X. Luo, *Molecular dynamics simulation investigation on the plastic flow behaviour of silicon during nanometric cutting*. Modelling and Simulation in Materials Science and Engineering, 2015. **24**(1): p. 015002.

- 4. Chavoshi, S.Z. and X. Luo, *An atomistic simulation investigation on chip related phenomena in nanometric cutting of single crystal silicon at elevated temperatures.* Computational Materials Science, 2016. **113**: p. 1-10.

- 5. Chavoshi, S.Z., S. Xu, and X. Luo, *Dislocation-mediated plasticity in silicon during nanometric cutting: A molecular dynamics simulation study.* Materials Science in Semiconductor Processing, 2016. **51**: p. 60-70.

- 6. Gogotsi, Y., G. Zhou, S.-S. Ku, and S. Cetinkunt, *Raman microspectroscopy analysis of pressure-induced metallization in scratching of silicon*. Semiconductor science and technology, 2001. **16**(5): p. 345-352.

- 7. Chavoshi, S.Z. and X. Luo, *Molecular dynamics simulation study of deformation mechanisms in 3C–SiC during nanometric cutting at elevated temperatures.* Materials Science and Engineering: A, 2016. **654**: p. 400-417.

- 8. Chavoshi, S.Z. and X. Luo, *Atomic-scale characterization of occurring phenomena during hot nanometric cutting of single crystal 3C-SiC.* RSC Advances, 2016. **6**: p. 71409-71424.

- 9. Chavoshi, S.Z. and X. Luo, Molecular dynamics simulation investigation of hot nanometric cutting of single crystal silicon, in Proceedings of the 16th International Conference of the European Society for Precision Engineering and Nanotechnology, EUSPEN 2016: Nottingham, UK.

- 10. Fang, T.-H., C.-I. Weng, and J.-G. Chang, *Molecular dynamics analysis of temperature effects on nanoindentation measurement*. Materials Science and Engineering: A, 2003. **357**(1): p. 7-12.

- 11. Liu, C.-L., T.-H. Fang, and J.-F. Lin, *Atomistic simulations of hard and soft films under nanoindentation*. Materials Science and Engineering: A, 2007. **452**: p. 135-141.

- 12. Hsieh, J.-Y., S.-P. Ju, S.-H. Li, and C.-C. Hwang, *Temperature dependence in nanoindentation of a metal substrate by a diamondlike tip.* Physical Review B, 2004. **70**(19): p. 195424-195433.

- 13. Atkins, A. and D. Tabor. *Hardness and deformation properties of solids at very high temperatures*. in *Proceedings of the Royal Society of London A: Mathematical, Physical and Engineering Sciences*. 1966. The Royal Society.

- 14. Wheeler, J., D. Armstrong, W. Heinz, and R. Schwaiger, *High temperature nanoindentation: The state of the art and future challenges.* Current Opinion in Solid State and Materials Science, 2015. **19**(6): p. 354-366.

- 15. Wheeler, J., P. Brodard, and J. Michler, *Elevated temperature, in situ indentation with calibrated contact temperatures.* Philosophical Magazine, 2012. **92**(25-27): p. 3128-3141.

- 16. Wheeler, J. and J. Michler, *Elevated temperature, nano-mechanical testing in situ in the scanning electron microscope*. Review of Scientific Instruments, 2013. **84**(4): p. 045103-045118.

- 17. Schuh, C.A., C.E. Packard, and A.C. Lund, *Nanoindentation and contact-mode imaging at high temperatures*. Journal of materials research, 2006. **21**(03): p. 725-736.

- 18. Trenkle, J.C., C.E. Packard, and C.A. Schuh, *Hot nanoindentation in inert environments*. Review of Scientific Instruments, 2010. **81**(7): p. 073901-073914.

- 19. Suzuki, T. and T. Ohmura, *Ultra-microindentation of silicon at elevated temperatures*. Philosophical Magazine A, 1996. **74**(5): p. 1073-1084.

- 20. Smith, J. and S. Zheng, *High temperature nanoscale mechanical property measurements*. Surface Engineering, 2000. **16**(2): p. 143-146.

- 21. Beake, B.D. and J.F. Smith, *High-temperature nanoindentation testing of fused silica and other materials.* Philosophical Magazine A, 2002. **82**(10): p. 2179-2186.

- 22. Xia, J., C. Li, and H. Dong, *Hot-stage nano-characterisations of an iron aluminide*. Materials Science and Engineering: A, 2003. **354**(1): p. 112-120.

- 23. Lund, A.C., A.M. Hodge, and C.A. Schuh, *Incipient plasticity during nanoindentation at elevated temperatures*. Applied physics letters, 2004. **85**(8): p. 1362-1364.

- 24. Schuh, C.A., A.C. Lund, and T. Nieh, New regime of homogeneous flow in the deformation map of metallic glasses: elevated temperature nanoindentation experiments and mechanistic modeling. Acta Materialia, 2004. **52**(20): p. 5879-5891.

- 25. Sawant, A. and S. Tin, *High temperature nanoindentation of a Re-bearing single crystal Ni-base superalloy.* Scripta materialia, 2008. **58**(4): p. 275-278.

- 26. Trelewicz, J.R. and C.A. Schuh, *Hot nanoindentation of nanocrystalline Ni–W alloys.* Scripta Materialia, 2009. **61**(11): p. 1056-1059.

- 27. Beake, B., J. Smith, A. Gray, G. Fox-Rabinovich, S. Veldhuis, and J. Endrino, Investigating the correlation between nano-impact fracture resistance and hardness/modulus ratio from nanoindentation at  $25-500^{\circ}$  C and the fracture resistance and lifetime of cutting tools with Ti 1-x Al x N (x=0.5 and 0.67) PVD coatings in milling operations. Surface and Coatings Technology, 2007. **201**(8): p. 4585-4593.

- 28. Beake, B.D., G. Fox-Rabinovich, S. Veldhuis, and S. Goodes, *Coating optimisation for high speed machining with advanced nanomechanical test methods*. Surface and Coatings Technology, 2009. **203**(13): p. 1919-1925.

- 29. Bhakhri, V. and R. Klassen, *Investigation of high-temperature plastic deformation using instrumented microindentation tests. Part IThe deformation of three aluminum alloys at 473 K to 833 K.* Journal of materials science, 2006. **41**(8): p. 2259-2270.

- Fox-Rabinovich, G., S. Veldhuis, G. Dosbaeva, K. Yamamoto, A. Kovalev, D. Wainstein, I. Gershman, L. Shuster, and B. Beake, *Nanocrystalline coating design for extreme applications based on the concept of complex adaptive behavior*. Journal of Applied Physics, 2008. **103**(8): p. 083510-083520.

- 31. Giuliani, F., A. Goruppa, S. Lloyd, D. Teer, and W. Clegg. *Indentation of AlN/CrN Multilayers from Room Temperature to 400° C.* in *Materials Science Forum.* 2005. Trans Tech Publ.

- 32. Gray, A. and B.D. Beake, *Elevated temperature nanoindentation and viscoelastic behaviour of thin poly (ethylene terephthalate) films.* Journal of nanoscience and nanotechnology, 2007. **7**(7): p. 2530-2533.

- Liu, Y., J. Teo, S. Tung, and K. Lam, *High-temperature creep and hardness of eutectic 80Au/20Sn solder*. Journal of Alloys and Compounds, 2008. 448(1): p. 340-343.

- 34. Packard, C.E., J. Schroers, and C.A. Schuh, *In situ measurements of surface tensiondriven shape recovery in a metallic glass.* Scripta Materialia, 2009. **60**(12): p. 1145-1148.

- 35. Schuh, C., J. Mason, and A. Lund, *Quantitative insight into dislocation nucleation* from high-temperature nanoindentation experiments. Nature Materials, 2005. **4**(8): p. 617-621.

- 36. Wood, A.M. and T. Clyne, *Measurement and modelling of the nanoindentation response of shape memory alloys.* Acta materialia, 2006. **54**(20): p. 5607-5615.

- 37. Bhuyan, S., J. Bradby, S. Ruffell, B. Haberl, C. Saint, J. Williams, and P. Munroe, *Phase stability of silicon during indentation at elevated temperature: evidence for a direct transformation from metallic Si-II to diamond cubic Si-I.* MRS Communications, 2012. **2**(01): p. 9-12.

- 38. Ruffell, S., J. Bradby, J. Williams, D. Munoz-Paniagua, S. Tadayyon, L. Coatsworth, and P. Norton, *Nanoindentation-induced phase transformations in silicon at elevated temperatures*. Nanotechnology, 2009. **20**(13): p. 135603-135608.

- 39. Domnich, V., Y. Aratyn, W.M. Kriven, and Y. Gogotsi, *Temperature dependence of silicon hardness: experimental evidence of phase transformations*. Rev. Adv. Mater. Sci, 2008. **17**: p. 33-41.

- 40. Gerbig, Y., S. Stranick, D. Morris, M. Vaudin, and R. Cook, *Effect of crystallographic orientation on phase transformations during indentation of silicon*. Journal of Materials Research, 2009. **24**(03): p. 1172-1183.

- 41. Wu, H., Fundamental investigations of cutting of silicon for photovoltaic applications. 2012, Georgia Institute of Technology.

- 42. Youn, S. and C. Kang, *FEA study on nanodeformation behaviors of amorphous silicon and borosilicate considering tip geometry for pit array fabrication*. Materials Science and Engineering: A, 2005. **390**(1): p. 233-239.

- 43. Li, Z.P., H. Zhao, and F.H. Zhang. Study on the Ductile Removal Behavior of K9 Glass with Nano-Scratch. in Advanced Materials Research. 2016. Trans Tech Publ.

- 44. Williams, J., *Analytical models of scratch hardness*. Tribology international, 1996. **29**(8): p. 675-694.

- 45. Briscoe, B.J., E. Pelillo, and S.K. Sinha, *Scratch hardness and deformation maps for polycarbonate and polyethylene*. Polymer Engineering & Science, 1996. **36**(24): p. 2996-3005.

- 46. Piltz, R., J. Maclean, S. Clark, G. Ackland, P. Hatton, and J. Crain, *Structure and properties of silicon XII: a complex tetrahedrally bonded phase*. Physical Review B, 1995. **52**(6): p. 4072-4085.

- 47. Ge, D., V. Domnich, and Y. Gogotsi, *High-resolution transmission electron microscopy study of metastable silicon phases produced by nanoindentation*. Journal of applied physics, 2003. **93**(5): p. 2418-2423.

- Gassilloud, R., C. Ballif, P. Gasser, G. Buerki, and J. Michler, *Deformation mechanisms of silicon during nanoscratching*. physica status solidi (a), 2005. 202(15): p. 2858-2869.

- 49. Domnich, V. and Y. Gogotsi, *Handbook of surface and interface of materials*. 2001, New York: Academic Press.

- 50. Ruffell, S., J. Bradby, and J.S. Williams, *Annealing kinetics of nanoindentation-induced polycrystalline high pressure phases in crystalline silicon*. Appl. Phys. Lett., 2007. **90**: p. 131901-131904.

- 51. Zeng, Z., Q. Zeng, W.L. Mao, and S. Qu, *Phase transitions in metastable phases of silicon*. Journal of Applied Physics, 2014. **115**(10): p. 103514-103520.

- 52. Olson, G. and J. Roth, *Kinetics of solid phase crystallization in amorphous silicon*. Materials Science Reports, 1988. **3**(1): p. 1-77.

- 53. Donnelly, S., R. Birtcher, V. Vishnyakov, and G. Carter, *Annealing of isolated amorphous zones in silicon*. Applied physics letters, 2003. **82**(12): p. 1860-1862.

- 54. Donnelly, S.E., R. Birtcher, V. Vishnyakov, P. Edmondson, and G. Carter, Anomalous annealing behavior of isolated amorphous zones in silicon. Nuclear

Instruments and Methods in Physics Research Section B: Beam Interactions with Materials and Atoms, 2006. **242**(1): p. 595-597.

- 55. Zhang, Z., J. Yan, and T. Kuriyagawa, *Study on tool wear characteristics in diamond turning of reaction-bonded silicon carbide*. The International Journal of Advanced Manufacturing Technology, 2011. **57**(1-4): p. 117-125.

- 56. Vogelgesang, R., A. Alvarenga, H. Kim, A. Ramdas, S. Rodriguez, M. Grimsditch, and T. Anthony, *Multiphonon Raman and infrared spectra of isotopically controlled diamond*. Physical Review B, 1998. **58**(9): p. 5408-5416.

- 57. Bachmann, P.K. and D.U. Wiechert, *Optical characterization of diamond*. Diamond and Related Materials, 1992. **1**(5): p. 422-433.

Accepted manuscring