# Fullerene-based spin-on-carbon hardmask

Frommhold, A.; Manyam, J.; Palmer, R.E.; Robinson, A.P.G

DOI:

10.1016/j.mee.2012.07.019

License:

None: All rights reserved

Document Version Publisher's PDF, also known as Version of record

Citation for published version (Harvard):

Frommhold, A, Manyam, J, Palmer, RÉ & Robinson, APG 2012, 'Fullerene-based spin-on-carbon hardmask', Microelectronic Engineering, vol. 98, pp. 552-555. https://doi.org/10.1016/j.mee.2012.07.019

Link to publication on Research at Birmingham portal

**Publisher Rights Statement:**

Eligibility for repository: checked 26/02/2014

General rights

Unless a licence is specified above, all rights (including copyright and moral rights) in this document are retained by the authors and/or the copyright holders. The express permission of the copyright holder must be obtained for any use of this material other than for purposes

- •Users may freely distribute the URL that is used to identify this publication.

- •Users may download and/or print one copy of the publication from the University of Birmingham research portal for the purpose of private study or non-commercial research.

•User may use extracts from the document in line with the concept of 'fair dealing' under the Copyright, Designs and Patents Act 1988 (?)

- •Users may not further distribute the material nor use it for the purposes of commercial gain.

Where a licence is displayed above, please note the terms and conditions of the licence govern your use of this document.

When citing, please reference the published version.

Take down policy

While the University of Birmingham exercises care and attention in making items available there are rare occasions when an item has been uploaded in error or has been deemed to be commercially or otherwise sensitive.

If you believe that this is the case for this document, please contact UBIRA@lists.bham.ac.uk providing details and we will remove access to the work immediately and investigate.

Download date: 18. Apr. 2024

Contents lists available at SciVerse ScienceDirect

# Microelectronic Engineering

journal homepage: www.elsevier.com/locate/mee

## Fullerene-based spin-on-carbon hardmask

A. Frommhold a,b, J. Manyam a, R.E. Palmer A, A.P.G. Robinson b,\*

<sup>a</sup> Nanoscale Physics Research Laboratory, School of Physics and Astronomy, University of Birmingham, Birmingham B15 2TT, UK

### ARTICLE INFO

Article history: Available online 20 July 2012

Keywords: Spin-on carbon Hardmask Fullerene ICP Silicon etching

#### ABSTRACT

As feature sizes have diminished the need for extremely thin photoresist films has grown. Given the poor selectivity of typical resists with respect to silicon during plasma etching, it has become common to use an intermediate hardmask to transfer the pattern. Furthermore the use of trilayer etch stacks to amplify the achievable etch aspect ratio is becoming increasingly popular for critical layers. Here we introduce a new fullerene based spin-on-carbon layer for use in a multilayer etch stack. Carbon films of between 20 and 1270 nm were prepared by spin coating. Thin silicon films were deposited on the carbon layer and patterned using a thin photoresist. Patterns were transferred to the carbon layer with high anisotropy at resolutions down to 40 nm using an oxygen plasma, and then subsequently etched into the silicon substrate using an  $SF_6/C_4F_8$  etch with high aspect ratio.

© 2012 Elsevier B.V. All rights reserved.

#### 1. Introduction

The minimum feature size required by semiconductor devices has continued to shrink to enable increasing chip density, with '2× nm' flash and logic devices now available. As the resolution requirements have increased it has become necessary to adopt extremely thin photoresist films to mitigate problems such as mechanical collapse of resist features upon development [1]. We have previously demonstrated a high resolution, high sensitivity and high etch durability fullerene resist [2] capable of aspect ratios greater than 5:1 for 25 nm lines and spaces [3]. However, even with such a resist the overall etch depth is limited by the usable resist thickness. The use of a multilayer hardmask stack allows further increase of the achievable etching aspect ratio. Typically such a multilayer stack is formed by first coating the wafer with a thick amorphous carbon layer using chemical vapor deposition (CVD), and then overlaying this with a thin-silicon rich layer, which may either be spin coated or prepared by CVD [4,5]. Finally photoresist is spin coated on top of the silicon layer. A thin photoresist film is sufficient to pattern the thin silicon layer, avoiding pattern collapse issues, and the silicon is used as a hard mask to pattern the underlying carbon, giving a high aspect ratio carbon pattern suitable for subsequent etching of the silicon wafer. By alternating from silicon to carbon rich materials and vice versa the overall etch selectivity can be maximized. In order to improve manufacturability and decrease costs it would be beneficial to replace the use of chemical vapor deposition with spin-on hardmasks (both silicon and carbon) [6,7]. Previously a novolac:HSQ bilayer stack achieved 40 nm half-pitch resolution with an aspect ratio of 3.25:1 as well as isolated 40 nm lines with an aspect ratio of 20:1 [8]. However, distortion of the spin-on-carbon features during the final fluorine etch to silicon step, known as 'wiggling', is a significant concern for sub 40 nm patterning [9]. Glodde et al. have recently proposed that the absence of aliphatic hydrocarbons in the carbon layer can reduce 'wiggling' [10]. Here we present an initial study of several fullerene-based 'spin-on-carbons' (SoC) with very low levels of aliphatic hydrocarbons. In addition spin-on-hard-masks can suffer from low etching resistance [11], but the carbon-rich nature of the fullerene based SoC gives high etch durability.

### 2. Experimental

Silicon (100) substrates (Rockwood Electronic Materials, n-type) were used for all experimental procedures. Square chips, 2 by 2 cm in size, were cut from a wafer using a Disco DAD 321 wafer dicer. The samples were cleaned using semiconductor grade chemicals from Riedel-de Haën. Samples were washed ultrasonically for 15 min in isopropyl alcohol (IPA), then rinsed for 1 min in deionized (DI) water (Purite Neptune, 18.2 M $\Omega$ cm). A hydrogen terminated surface was then prepared by dipping the substrates in H<sub>2</sub>SO<sub>4</sub> (95–98%):H<sub>2</sub>O<sub>2</sub> for 10 min, DI water for 1 min and dilute HF for 1 min, then rinsing in DI water for a further minute before drying with nitrogen. Substrates were stored under vacuum after preparation and used within 2 days.

We evaluated three spin-on carbon hardmasks from Irresistible Materials [12]. The spin-on carbon compositions were dissolved in a suitable solvent such as chloroform or anisole with a

<sup>&</sup>lt;sup>b</sup> School of Chemical Engineering, University of Birmingham, Birmingham B15 2TT, UK

<sup>\*</sup> Corresponding author. Tel.: +44 121 414 4641; fax: +44 121 414 7327. E-mail address: a.p.g.robinson@bham.ac.uk (A.P.G. Robinson).

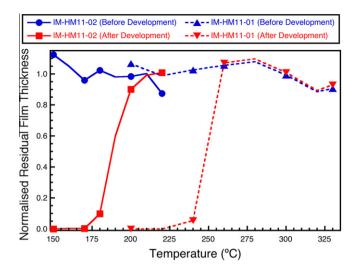

**Fig. 1.** The normalized film thickness of SoC films IM-HM11-01 and IM-HM11-02 before and after 'development' in an organic solvent (MCB:IPA 1:1). For temperatures above 190  $^{\circ}$ C IM-HM11-02 was not removed by the solvent rinse, whilst a temperature of 260  $^{\circ}$ C was required to render the IM-HM11-01 SoC insoluble.

concentration in the range 5-50 g/l. In this report, film thickness measurements were made for IM-HM11-01 and IM-HM11-02 films, whilst IM-HM11-03 was used for etching: further investigations to compare the performance of the different compositions across tasks are underway. Films of the SoC were prepared by spin coating on hydrogen-terminated silicon substrates with a speed varying between 800 and 2000 RPM for 60 s. After spin coating the film was baked for 2 min at temperatures of up to 330 °C. In order to enable further processing, the SoC should be rendered insoluble in typical solvents for resist and spin-on-hardmask to enable further processing. The elution behavior of films of IM-HM11-01 and IM-HM11-02 for thicknesses between 30 and 325 nm was tested as a function of the baking temperature. Fig. 1 shows the normalized film thickness of two formulations of the SoC (IM-HM11-01 and IM-HM11-02), before and after dipping in monochlorobenzene (MCB):IPA 1:1 solution. Prior to baking the thickness of IM-HM11-01 was ∼320 nm, and the thickness of IM-HM11-02 was ~250 nm. For temperatures above 190 °C the IM-HM11-02 film was rendered insoluble, whilst a temperature of 260 °C was required to achieve the same for IM-HM11-01. Film thickness did not affect the elution results.

By varying the spin coating conditions and the concentration of the spin-on-carbon solution, films from 20 to 325 nm could be prepared in a single spin coating step. After coating films were stored in Entegris chip trays under ambient conditions in a cleanroom. No

**Table 1**AFM roughness measurements of two IM-HM11-01 films and a reference sample of silicon

|                               | IM-HM11-01      | IM-HM11-01      | Bare    |

|-------------------------------|-----------------|-----------------|---------|

|                               | baked at 225 °C | baked at 375 °C | silicon |

| Average roughness (nm)        | 0.49            | 0.35            | 0.28    |

| RMS roughness (nm)            | 0.60            | 0.45            | 0.35    |

| Peak-to-valley roughness (nm) | 7.24            | 4.50            | 4.57    |

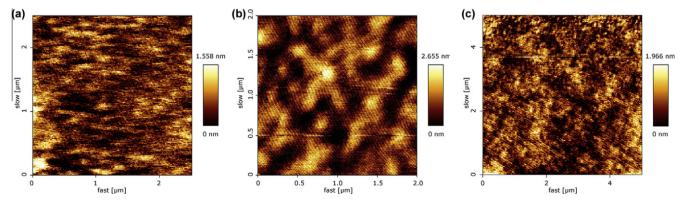

degradation of performance was seen even after more than a month of storage. The quality of the films was measure using a NanoWizard II atomic force microscope (JPK Instruments, UK) operating in intermittent contact mode at a tip velocity of 4  $\mu$ m/s, employing pyramidal tipped Si cantilevers (PPP-NCL, Windsor Scientific, UK). Fig. 2(a) shows an AFM image of a typical bare Silicon substrate, and Fig. 2(b) and (c) shows SoC films baked at 225 and 375 °C respectively. It can be seen from the figure and from Table 1 that the SoC does not significantly degrade the smoothness of the silicon.

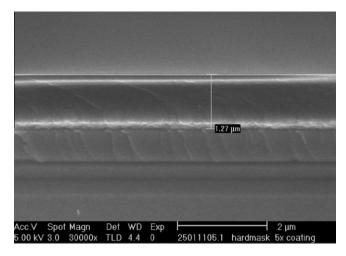

As the carbon was rendered insoluble by heating it was possible to spin coat further carbon on top to increase the thickness. Fig. 3 shows an SEM (FEI XL30 SFEG) cross section of a carbon film of thickness 1.27 microns prepared by spinning five (IM-HM11-03) films of thickness ~250 nm on top of a each other with a heating step of 330 °C for 5 min between each spin coating.

After preparation of a  $\sim$ 300 nm IM-HM11-03 carbon film. a 40 nm thick silicon layer was deposited by sputtering at an argon pressure of  $1 \times 10^{-2}$  mbar for 2 min with 250 W RF power. Alternatively, Plasma Enhanced Chemical Vapour Deposition (PECVD) could be used to deposit the silicon film. Finally a photoresist was spin coated on top of the silicon layer. For this study either SAL601 (Shipley) or an in-house fullerene based resist were used. A post application bake of 90 °C for 10 min was applied to the SAL601; no post application bake was applied to the fullerene resist. The resist was patterned using an FEI XL30 SFEG scanning electron microscope equipped with a pattern generator (Raith Elphy Plus). SAL601 was exposed with an area dose 20 μC/cm<sup>2</sup> whilst the fullerene was exposed with a line dose of 10 nC/cm  $(\sim 1.5 \text{ mC/cm}^2)$ . The SAL601 received a post exposure bake of 105 °C for 2 min and no post exposure bake was applied to the fullerene. Finally SAL601 was developed for 5 min in MF322 (Shipley) whilst the fullerene was developed in a 1:1 mixture of MCB:IPA. 80 nm halfpitch patterns and 40 nm sparse lines were patterned and then etched into the silicon thin film using an Oxford Instruments PlasmaPro NGP80 Inductively Coupled Plasma (ICP) etching system. Silicon substrates were attached using vacuum grease to a sacrificial silicon wafer to ensure good thermal contact. The sacrificial wafer was mechanically clamped to the lower electrode,

Fig. 2. AFM images of (a) reference sample of bare silicon, (b) an IM-HM11-01 film baked at 225 °C respectively, and (c) an IM-HM11-01 film baked at 375 °C.

**Fig. 3.** SEM cross section of a SoC film of thickness 1.27 nm produced by spin coating five films consecutively with a heating step between each coating.

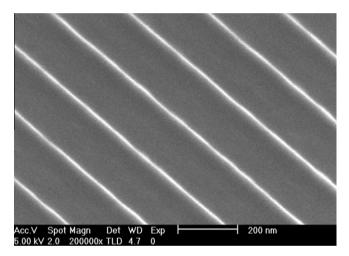

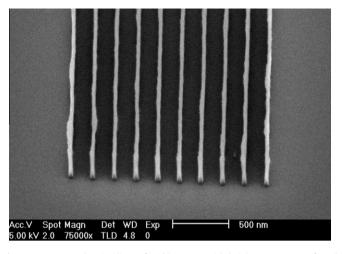

**Fig. 4.** Lines of 40 nm width transferred from a thin resist film into the silicon topcoat using an ICP etch. SEM image tilt is 45°.

which is equipped with helium backside pressure to ensure good thermal control of the sample during the etching process. The pattern was transferred into the silicon topcoat using a 20 s mixed mode  $SF_6/C_4F_8$  ICP etch.  $SF_6$  flow rate was 25 sccm and  $C_4F_8$  flow rate 30 sccm. An RF power of 20 W and ICP power of 220 W were applied. Chamber pressure was 15 mT and the temperature was 1 °C. Fig. 4 shows 40 nm lines on a 200 nm pitch etched into the silicon on top of the SoC.

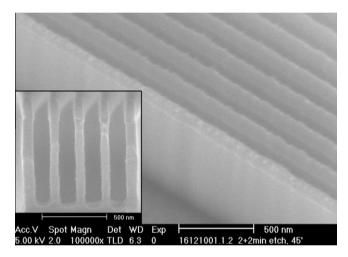

To transfer the pattern from the silicon to the IM-HM11-03 SoC an oxygen plasma etch was used. The selectivity of the silicon hardmask with respect to the carbon for oxygen plasma is extremely high, allowing transfer to thick carbon films. In order to minimize undercutting of the carbon, and maintain vertical sidewalls during the etch, a low chamber pressure was needed, and it was necessary to end the etch as soon as the etch depth reached the substrate or severe undercutting was seen at the SoC foot. Fig. 5 shows lines of 38 nm width on a 200 nm pitch etched through a 260 nm thick SoC film. Etch duration was 20 s with an O<sub>2</sub> flow rate of 15 sccm. RF power of 100 W and ICP power of 300 W were applied. Chamber pressure was 2 mT and the temperature was 1 °C.

The final step was to transfer the carbon hard mask pattern into the silicon substrate with another mixed mode  $SF_6/C_4F_8$  ICP etch.

**Fig. 5.** SEM image showing lines of width 38 nm, with height 260 nm, transferred to the SoC by oxygen plasma etching. SEM image tilt is  $44^{\circ}$ .

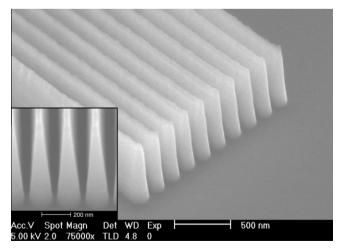

**Fig. 6.** Lines of 60 nm width and 700 nm height (aspect ratio 11.6:1) etched into the silicon substrate, using a mixed  $SF_6/C_4F_8$  etch.

Fig. 7. Lines of 40 nm width and 718 nm height (aspect ratio 18:1) etched into the silicon substrate, using a mixed  $SF_6/C_4F_8$  etch.

For semi-dense 60 nm lines silicon features with an aspect ratio of 11:1 were produced, as shown in Fig. 6, whilst for 40 nm linewidth features on a 200 nm pitch an aspect ratio of 18:1 (linewidth

measured at the top) were produced, as shown in Fig. 7. In both cases the mixed mode  $SF_6/C_4F_8$  ICP etch parameters used were:  $SF_6$  flow rate 20 sccm,  $C_4F_8$  flow rate 30 sccm, RF power 20 W, ICP power 220 W. Chamber pressure was 15 mT. It can be seen from the inserts to Figs. 6 and 7 that the sidewall verticality is significantly degraded for the 40 nm features. Apart from the feature size the primary difference was that Fig. 6 was etched at 5 °C, whilst Fig. 7 was etched at 1 °C. Further optimization of the parameters for the 40 nm etch is required.

#### 3. Conclusions

In summary, initial work on the development of a fullerenederivative based spin-on-carbon material, aimed at increasing the achievable aspect ratio for sub-100 nm etching, has been presented. Films rich in aromatic carbon, from 20 to 325 nm in thickness, have been prepared by spin coating. A post-spin bake step renders the material insoluble in common organic solvents enabling further spin coating, and a multilayer carbon film of 1270 nm thickness has been prepared. Using a sputter coated thin silicon topcoat and a thin (30-100 nm) photoresist film, patterns with a linewidth of 40 nm have been transferred to the carbon layer with good sidewall verticality. Preliminary results of etching from the SoC pattern to the silicon substrate have shown 60 nm features etched with an aspect ratio in excess of 11:1. Smaller features have also successfully been transferred from the SoC to the substrate, but further work is required to optimize the sidewall angle. Using a suitable formulation of the fullerene SoC, the activation temperature for hardening can be as low at 190 °C - compatible with other microfabrication processes. Unlike current CVD approaches to the preparation of multilaver etch stacks the application process is simple, quick and does not require expensive deposition equipment. In comparison to polymers used in other SoC approaches fullerene is inherently low in hydrogen content, which has been shown to be key to reducing feature 'wiggling' as pattern halfpitch decreases [10]. The etch durability of fullerene based resists, described elsewhere [3], together with the high fidelity transfer of 40 nm patterns to the SoC layer suggest that aspect ratios in excess of 30:1 at feature sizes of 40 nm or less may be achievable.

#### Acknowledgements

The authors thank the Engineering and Physical Sciences Research Council (EPSRC) for support of this project. The Disco DAD 321 wafer dicer and the Oxford Instruments PlasmaPro NGP80 Inductively Coupled Plasma etching system used in this research were obtained, through Birmingham Science City: Creating and Characterising Next Generation Advanced Materials, with support from Advantage West Midlands (AWM) and part funded by the European Regional Development Fund (ERDF). The atomic force microscope used in this research was obtained, through Birmingham Science City: Innovative Uses for Advanced Materials in the Modern World (West Midlands Centre for Advanced Materials Project 2), with support from Advantage West Midlands (AWM) and part funded by the European Regional Development Fund (ERDF). We thank Dr J. Bowen for his assistance with the AFM measurements. JM thanks the Royal Thai Government for the award of a scholarship.

#### References

- W.-M. Yeh, R.A. Lawson, L.M. Tolbert, C.L. Henderson, Proc. SPIE 7972 (2011) 79721Y.

- [2] F.P. Gibbons, A.P.G. Robinson, S. Diegoli, M. Manickam, J.A. Preece, R.E. Palmer, Adv. Funct. Mater. 18 (2008) 1977.

- [3] J. Manyam, M. Manickam, J.A. Preece, R.E. Palmer, A.P.G. Robinson, Proc. SPIE 7972 (2011) 79722N.

- [4] S. Pauliac-Vaujour, P. Brianceau, C. Comboroure, O. Faynot, Microelectron. Eng. 85 (2008) 800.

- [5] C.-Y. Ho, X.J. Lin, H.R. Chien, C. Lien, Thin Solid Films 518 (2010) 6076.

- [6] Z. Zhu, E. Piscani, Y. Wang, J. Macie, C.J. Neef, B. Smith, Proc. SPIE Vol. 7274 (2009) 72742K.

- [7] Y. Wei, M. Glodde, H. Yusuff, M. Lawson, S.Y. Chang, K.S. Yoon, C.-H. Wu, M. Kelling, Proc. SPIE 7972 (2011) 79722L.

- [8] F.C.M.J.M. van Delft, J.P. Weterings, A.K. van Langen-Suurling, H. Romijn, J. Vac. Sci. Technol. B 18 (2000) 3419.

- [9] M. Tadokoro, K. Yonekura, K. Yoshikawa, Y. Ono, T. Ishibashi, T. Hanawa, N. Fukiwara, T. Matsunobe, K. Matsuda, J. Vac. Sci. Technol. B 26 (2008) 67.

- [10] M. Glodde, S. Engelmann, M. Guillorn, S. Kanakasabapathy, E. Mclellan, C.-S. Koay, Y. Yin, M. Sankarapandian, J.C. Arnold, K. Petrillo, M. Brink, H. Miyazoe, E.A. de Silva, H. Yusuff, K.-S. Yoon, Y. Wei, C.-H.J. Wu, P.R. Varanasi, Proc. SPIE 7972 (2011) 797216.

- [11] M. Muramatsu, M. Iwashita, T. Kondo, H. Hirose, S. Fujimoto, Proc. SPIE 7972 (2011) 797226.

- [12] Irresistible Materials Ltd., available from: <a href="http://www.irresistiblematerials.com">http://www.irresistiblematerials.com</a>.