# UNIVERSITY<sup>OF</sup> BIRMINGHAM University of Birmingham Research at Birmingham

# High aspect ratio silicon and polyimide nanopillars by combination of nanosphere lithography and intermediate mask pattern transfer

Frommhold, Andreas; Robinson, Alex; Tarte, Edward

DOI: 10.1016/j.mee.2012.06.008

License: None: All rights reserved

Document Version Publisher's PDF, also known as Version of record

Citation for published version (Harvard):

Frommhold, A, Robinson, A & Tarte, E 2012, 'High aspect ratio silicon and polyimide nanopillars by combination of nanosphere lithography and intermediate mask pattern transfer', *Microelectronic Engineering*, vol. 99, pp. 43-49. https://doi.org/10.1016/j.mee.2012.06.008

Link to publication on Research at Birmingham portal

Publisher Rights Statement: Eligibility for repository : checked 26/02/2014

### **General rights**

Unless a licence is specified above, all rights (including copyright and moral rights) in this document are retained by the authors and/or the copyright holders. The express permission of the copyright holder must be obtained for any use of this material other than for purposes permitted by law.

•Users may freely distribute the URL that is used to identify this publication.

•Users may download and/or print one copy of the publication from the University of Birmingham research portal for the purpose of private study or non-commercial research.

•User may use extracts from the document in line with the concept of 'fair dealing' under the Copyright, Designs and Patents Act 1988 (?) •Users may not further distribute the material nor use it for the purposes of commercial gain.

Where a licence is displayed above, please note the terms and conditions of the licence govern your use of this document.

When citing, please reference the published version.

#### Take down policy

While the University of Birmingham exercises care and attention in making items available there are rare occasions when an item has been uploaded in error or has been deemed to be commercially or otherwise sensitive.

If you believe that this is the case for this document, please contact UBIRA@lists.bham.ac.uk providing details and we will remove access to the work immediately and investigate.

#### Microelectronic Engineering 99 (2012) 43-49

Contents lists available at SciVerse ScienceDirect

### Microelectronic Engineering

journal homepage: www.elsevier.com/locate/mee

## High aspect ratio silicon and polyimide nanopillars by combination of nanosphere lithography and intermediate mask pattern transfer

Andreas Frommhold<sup>a,b,\*</sup>, Alex P.G. Robinson<sup>b</sup>, Edward Tarte<sup>c</sup>

<sup>a</sup> Nanoscale Physics Research Laboratory, School of Physics and Astronomy, University of Birmingham, B152TT Birmingham, UK

<sup>b</sup> Department of Chemical Engineering, University of Birmingham, B152TT Birmingham, UK

<sup>c</sup> Department of Electrical, Electronics and Computer Engineering, University of Birmingham, B152TT Birmingham, UK

#### ARTICLE INFO

Article history Received 14 May 2012 Accepted 11 June 2012 Available online 23 June 2012

Keywords: ICP etching Nanopillars Hardmask High aspect ratio

1. Introduction

ABSTRACT

Silicon and polymer nanopillar structures with sub-100 nm diameter and high aspect ratios were fabricated using a modified nanosphere lithography process. A thin silicon film was sputtered onto spincoated polyimide films. A self-assembled layer of nanospheres was then formed on the silicon. Reactive ion etching with  $SF_6/C_4F_8$  was used to transfer the nanosphere pattern to the silicon. Oxygen plasma etching then transferred the silicon pattern into the polymer to create nanopillars. The nanopillar diameter could be finely tuned by oxygen plasma thinning of the nanospheres and the conditions for silicon mask etching. In the last step the polyimide pillars served as etch masks to transfer the structures back into the silicon substrate to give well-ordered pillars of 1.3 µm height and 75 nm diameter.

© 2012 Elsevier B.V. All rights reserved.

As the successful employment of high aspect ratio nanostructures in a diverse range of applications such as for example the ability to influence the propagation of light [1], catalyse chemical reactions [2], control the attachment of cells [3] or modify the wetting behaviour of bulk substrates [4] continues to grow, the ability to produce these with increasingly smaller lateral dimensions is highly desired. In particular one-dimensional structures such as pillars require a high degree of etch control and anisotropy as they are more prone to loss of features due to undercutting. The most common fabrication route for high aspect ratio nanostructures is the patterning of an etch mask by e-beam lithography on top of a silicon substrate in combination with a selective plasma etch process [5]. The durability of the etch mask in the plasma process is a key factor for achieving high aspect ratios and the use of novel materials such as alumina [6] have provided dramatic improvement. However, the serial patterning used in electron beam lithography is time consuming and requires expensive equipment.

Nanosphere lithography (NSL) [7,8] has established itself as a low cost, bench-top technique that offers an alternative approach to one-dimensional pillar-type structures. The self-assembled sphere arrays can either be used as shadow masks for the deposition of an etch mask such as silver [9] resulting in small diameter

triangular pillars or the silicon substrate can be etched directly through the nanosphere array [10]. The most common material for nanospheres is polystyrene as it offers monodisperse particles in a broad size range from around 20 nm to 10 µm and the sphere diameter is readily modified by oxygen plasma thinning after deposition. However, polystyrene spheres are quickly eroded by the etch gas used in common plasma etches and typically only low aspect ratios can be achieved. Other materials that have been successfully used for nanopillar fabrication include silica spheres [11] and colloidal gold particles [12]. Using NSL silicon nanopillars have been produced for applications such as field emission [13], antireflective coatings [14] and for producing hydrophobic surfaces [15]. Nonetheless it remains a challenge to achieve small, dense structures with larger aspect ratios.

In order to increase aspect ratio more complex etch processes have been utilised. One option is the use of the Bosch process, that cycles between an isotropic  $SF_6$  etch and the deposition of a passivation polymer layer from  $C_4F_8$  gas to provide anisotropy [16]. Using the Bosch process sub-500 nm diameter silicon pillars with aspect ratios up to 10 have been demonstrated [17]. A significant problem when applying this process to the nanoscale is the characteristic scalloping on the sidewall as a result of the isotropic etch step. This increases the sidewall roughness and severely limits the minimum feature size. A method becoming increasingly popular for nanoscale patterning is cryogenic etching [18]. Cooling the sample to temperatures around  $-110 \,^{\circ}$ C and using a SF<sub>6</sub>/O<sub>2</sub> gas combination provides smooth sidewalls and high anisotropy. The cryogenic temperatures favour the formation of a thin volatile SiO<sub>x</sub>F<sub>y</sub> passivation layer that protects the sidewalls during etching. However,

<sup>\*</sup> Corresponding author at: Nanoscale Physics Research Laboratory, School of Physics and Astronomy, University of Birmingham, B152TT Birmingham, UK,

E-mail addresses: a.frommhold@bham.ac.uk (A. Frommhold), a.p.g.robinson@bham.ac.uk (A.P.G. Robinson), tartee@adf.bham.ac.uk (E. Tarte).

<sup>0167-9317/\$ -</sup> see front matter © 2012 Elsevier B.V. All rights reserved. http://dx.doi.org/10.1016/j.mee.2012.06.008

this technique requires special equipment to provide the cryogenic cooling, and mask material choice is limited as masks are prone to cracking because of thermal stresses. Pillars etched by this process using NSL have recently been shown to exhibit aspect ratios up to 18:1 with 200 nm diameter [19].

Finally, the use of an oxide or metal hardmask, which is significantly more durable than the polystyrene in etching, can increase aspect ratio [20]. However inorganic hardmasks lead to significant problems themselves such as debris, sidewall roughening [21] and grass formation [22], interaction with polymer layer, scumming and pattern distortion due to stress [23], and diffusion of hardmask into the substrate [21]. Furthermore as resolution increases, removing inorganic hardmasks after processing (typically done with a wet etch which can lead to substrate damage [24] or feature collapse in high aspect ratio nanostructures) is becoming increasingly challenging.

As the progression towards smaller lithographic nodes continues it has become necessary to adopt thinner resist films to mitigate problems such as pattern collapse. To address the issue of reduced etch resistance of thin photoresist films the semiconductor industry has begun to develop multilayer processes where the pattern is first transferred into an intermediate organic hardmask with higher etch selectivity before final silicon pattern transfer [25–27]. In this paper we demonstrate how the introduction of such a multilayer process can also benefit nanosphere lithography by increasing achievable aspect ratios of silicon nanopillars without the need for complex etch processes requiring specialised and expensive equipment, but instead needing only a standard  $SF_6/C_4F_8$  inductively coupled plasma (ICP) mixed mode etch process at room temperature [28]. As intermediate layer material we used polyimide, which finds widespread use as encapsulation material for IC production. It is readily patterned in oxygen plasma and has a lower etch rate than silicon in SF<sub>6</sub> gas. Its flexibility can also be used for the fabrication of soft polymer pillars by the same process as we will show. The multilayer process slightly increases the complexity of sample preparation but allows basic ICP etching to achieve high aspect ratio structures at smaller feature sizes that previously reported without the need for complex etching equipment.

### 2. Experimental

The silicon substrates were pre-cleaned in isopropyl alcohol (IPA) in an ultrasonic bath to remove particles and organic residue followed by rinsing in de-ionised (DI) water. For polyimide nanopillars the substrate was coated with a 5 µm layer of PI2611 polyimide by spin coating at 6000 rpm. For high aspect ratio silicon pillar fabrication the polyimide was thinned by mixing equal proportions of PI2611 with N-methyl-2-pyrrolidone (NMP) to decrease the coating thickness and spun at 4500 rpm for a 350 nm thick layer. A 200 nm thin film of silicon was then sputtered onto the polyimide layer at 300 W at an argon pressure of 2 Pa for 10 min using an Edwards Auto 306 sputter coater. As nanosphere lithography requires a hydrophilic surface it is common to apply an additional surface treatment like immersion in a mixture of H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub> [29] before sphere deposition. However this is incompatible with the polyimide layer. Choosing a comparatively high sputter pressure for the deposition process we observe the silicon to be intrinsically hydrophilic so that no surface modification was necessary. We speculate that this behaviour is due to a porous film structure [30], commonly found for high sputter deposition pressures.

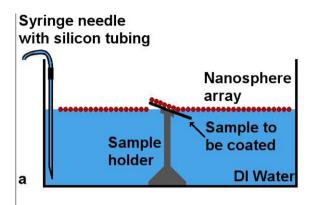

For nanosphere deposition we have developed our own technique illustrated in Fig. 1. The silicon to be coated was attached to a holder with carbon tape and completely immersed in a

Fig. 1. (a) Principle of nanosphere deposition and (b) experimental setup.

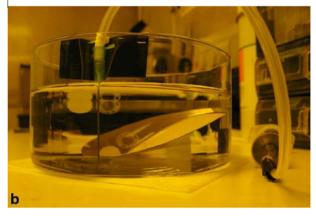

**Fig. 2.** (a) Uniform coverage of large area with spheres (scale bar 100  $\mu$ m; inset 10,000× magnification) and (b) optical image of sphere coated sample.

125 mm wide crystallising dish filled with DI water. Fifty microlitres of a 1:1 mixture of Thermo Scientific 200 nm 10 wt.%

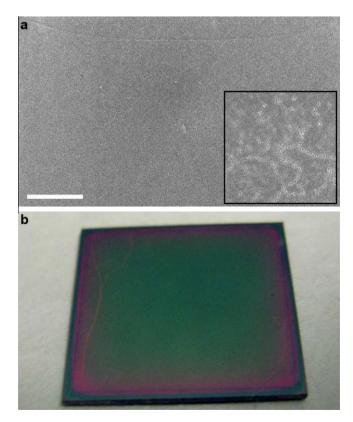

Fig. 3. Process schematic for pillar fabrication.

Fig. 4. Silicon pillars by etching through sphere template for 2 min etch time and (a) no prior oxygen pretreatment, (b) 15 s, (c) 30 s and (d) 60 s oxygen plasma.

nanosphere solution with ethanol was pipetted onto a second  $H_2SO_4$ : $H_2O_2$  cleaned silicon chip. The solution was allowed to spread for a few seconds before the nanosphere carrying silicon was slowly immersed into the water in the crystallising dish. During immersion the nanospheres lifted from the carrier and spread across the water–air interface due to the trapping effect of ethanol. Using a syringe needle with attached silicone tubing taped to the side of the dish the water was then slowly extracted. As the water

level sank below the silicon work piece the spheres were transferred to the sample surface with minimum perturbation, resulting in high quality sphere coating of the entire sample surface. Fig. 2 shows a SEM image of a large area with densely packed spheres without any voids or large-scale defects and a optical image of an entire silicon chip covered with the sphere layer visible as blue-green film typical for this sphere size. It is seen that apart from a crack running alongside the left edge the layer is homoge-

Fig. 5. Silicon pillar etch mask on top of a layer of polyimide.

nous. Several samples can be coated simultaneously within one deposition by placing them together in the same dish, as the spheres covered the entire surface of the water.

After evaporation of excess water trapped between sample surface and sphere array, the sample was transferred into an Oxford Instruments Plasmalab NGP80+ ICP/RF etcher. The sphere diameter was reduced by oxygen plasma etching at 100 W RF power and 30 sccm  $O_2$  flow at 20 °C and a pressure of 15 mTorr for various durations. Subsequently the spheres served as etch masks for etching the silicon thin film coating using a mixture of SF<sub>6</sub> and C<sub>4</sub>F<sub>8</sub> at 0 °C with 20 W RF power and 220 W ICP power for 2 min with an SF<sub>6</sub> flow rate of 20 sccm and 30 sccm C<sub>4</sub>F<sub>8</sub>, at a pressure of 15 mTorr.

The polyimide pillars were produced by etching the polyimide film through the patterned silicon layer in oxygen plasma with 100 W RF power and 100 W ICP power at 0 °C, an oxygen flow of 30 sccm and at a pressure of 5 mTorr. The thick polyimide for polyimide pillars was etched for up to 3 min while the thin layer was subjected to a shorter etch period of 45 s. For the production of high aspect ratio silicon pillars it has to be ensured that the polyimide is etched down until the silicon is exposed at the bottom. Finally a further silicon etch with a mixed  $SF_6$  and  $C_4F_8$  gas was employed for 5 min to produce high aspect ratio silicon pillars using the same silicon etch conditions as before. The process steps are illustrated in Fig. 3.

Fabricated structures were examined in a Philips XL30 SFEG scanning electron microscope (SEM) using a 45° sample holder in ultra high resolution mode. Contact angle measurements were performed with a Krüss Easy Drop.

#### 3. Results and discussion

#### 3.1. Direct patterning of the substrate from the nanosphere mask

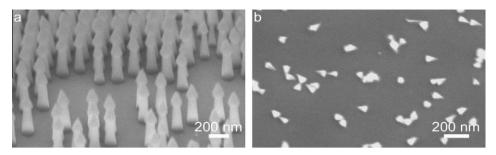

Bare silicon substrates with nanosphere assemblies on top were used to demonstrate the effect of altering the sphere diameter through oxygen plasma etching of the nanospheres prior to SF<sub>6</sub>/ C<sub>4</sub>F<sub>8</sub> etching of the silicon on the shape of the final silicon structures and the limited aspect ratio that can be achieved when using the spheres directly as etch masks. We define aspect ratio as the ratio of the height of the pillar to its diameter. Through oxygen plasma treatment the outer layers of the latex polymer spheres are removed, effectively reducing the sphere diameter while the silicon is unaffected by the short oxygen plasma etch times involved. The reduction of the sphere diameter exposes more silicon so that after pattern transfer from the spheres to the substrate using the SF<sub>6</sub>/C<sub>4</sub>F<sub>8</sub> etch the resulting silicon pillar diameter also decreases allowing for a straight forward engineering of the final pillar diameter. During the silicon etching the spheres are slowly eroded by the etchants but at a lower rate than silicon allowing for aspect ratios greater than one. However, when reducing the sphere diameter one also decreases the amount of polymer material covering the silicon reducing the achievable structure height.

Fig. 4 shows the results of varying the oxygen plasma etch duration on the silicon pillar dimensions, whilst maintaining the  $SF_6/C_4F_8$ etching conditions. It can clearly be seen how the diameter of, and spacing between, the pillars is affected by the oxygen plasma conditions. The shape of the features changes from dense packed cylindrical appearance to conical structures to well separated sharp needles.

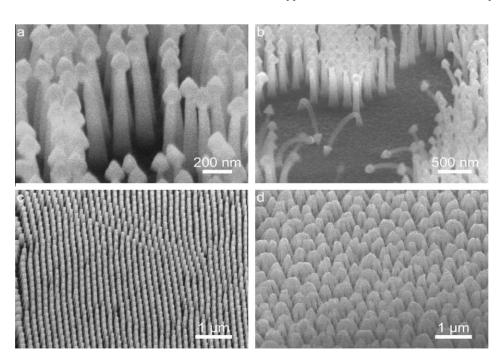

Fig. 7. SEM images of (a) polyimide etch mask and (b) detached silicon cones after release due to prolonged etching.

Fig. 8. SEM images of (a) an array of silicon pillars, (b) pillar tops, (c) side view of the pillar structures, (d) deformed pillars after wetting, (e) more uniform shape for lower etch depths and (f) onset of nonuniformity.

The needles are effectively produced as the sphere material protecting the silicon is slowly etched away during the  $SF_6/C_4F_8$  etch, leading to rapid pillar thinning, and placing a limit on the achievable aspect ratio. In some of the examples the remaining spheres are still visible on top of the structures (Fig. 4a and b).

### 3.2. Patterning of sputtered silicon thin film

In order to improve the achievable aspect ratio a polyimide/silicon thin film multilayer was prepared on the silicon substrate as described in the experimental section. A nanosphere mask was then formed on top of the multilayer stack, and used to pattern the sputtered silicon in a manner analogous to Section 3.1. The patterned sputtered silicon itself then serves as etch mask for the polyimide.

When preparing the sputtered silicon etch mask it must be ensured that the thin silicon film is completely removed in the unmasked areas. If the polyimide underneath is not fully exposed prior to oxygen plasma treatment it will not be etched due to the high durability of even a thin residual silicon film to oxygen etching. Fig. 5 shows a well resolved silicon etching mask created on the polyimide layer. The surface roughening of the bottom layer is indicative that the silicon mask has been opened and the SF<sub>6</sub> is slowly eroding the exposed polyimide. For device fabrication the area to be covered with pillars can be simply controlled by removing areas of the top silicon layer by photolithography and wet etching in tetra methyl ammonium hydroxide (TMAH) prior to sphere deposition allowing coarse features to be defined by photolithography and high resolution pillars by nanospheres. Whilst nanospheres will decorate the whole surface - including the polyimide exposed by photolithography - pillars will only be formed in areas where the silicon remains due to the similarity in etch selectivity of spheres and polyimide to oxygen plasma.

Fig. 9. Contact angle measurement on (a) bare silicon and (b) silicon pillars; (c) pillar surface after repeated wetting, (d) magnification of bundled pillars.

#### 3.3. Transfer of silicon thin film mask to polyimide layer

In the next step the sputtered silicon mask pattern was transferred into the polyimide layer by an inductively coupled plasma (ICP) oxygen etch. As the silicon is barely eroded by the oxygen plasma it provides an excellent etch mask for prolonged etch times to fabricate tall structures. The ICP's effect is to maintain a plasma of reactive species in low pressure conditions to ensure near-vertical sidewalls. For the same reason the sample is cooled to 0° to prevent the polyimide from heating and wilting.

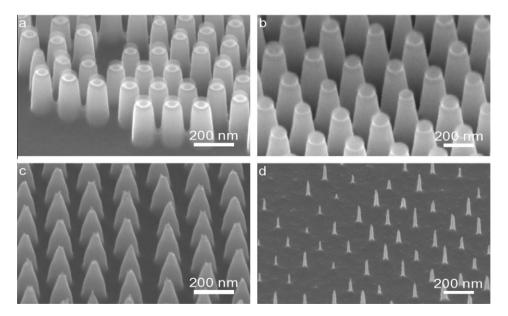

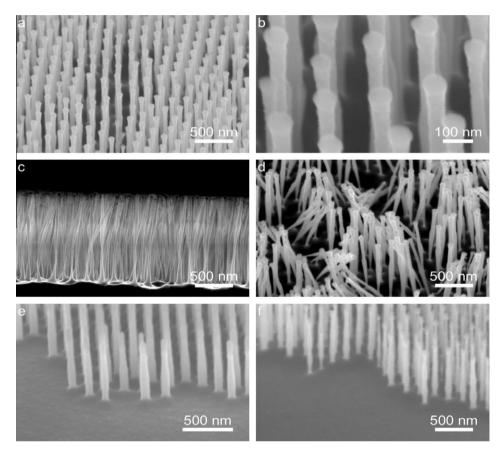

After etching the thick polyimide layer for 2 min, pillars with an average height of 600 nm were fabricated. After 3 min etch duration their height was 1.46 um. The structures appear conical indicating a slow undercutting of the mask. As seen in Fig. 6 the pillars are flexible enough to bend, which in this case is caused by charging of the dielectric polyimide with the electron beam of the SEM. After fabrication of the pillars the silicon mask on top has to be removed. Wet-etching the silicon with TMAH quickly removes the silicon but causes the pillars to bundle together because of surface tension effects and capillary interaction during drying [31,32]. This could be prevented by using supercritical drying after the etch. Alternatively a short silicon dry etch could be used to remove the silicon caps but had to be timed precisely because the etch also attacks the polyimide material. An etch time of 2 min was found to be enough to perform the removal. The bundled pillars have been coated with gold by thermal evaporation for successful surface area increase of planar surfaces for neural applications. Straight pillars are more difficult to coat as the small separation between the pillars does not allow sufficient flux from physical vapour deposition to reliably cover the pillar sidewalls. Future work will explore the deposition of metal by chemical vapour deposition to coat the individual pillars completely. This opens up further possible applications like nano-catalysis, mechanically flexible metal nanopillars and nanostructured electrodes for batteries. With the advent of organic electronics the pillar process could also be applied to conductive polymers to shape them into nanoscale patterns for next generation devices. Polymer pillars are more commonly produced by replication of a master through moulding [33]. Our process does not require the fabrication of a master or the use of imprint equipment and the dimensions of the pillars are readily adjusted by the etch parameters.

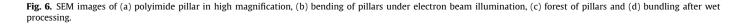

When using the thin polyimide layer for the second masking step careful timing has to be applied when etching the polyimide. Because the silicon substrate provides an effective etch stop to the oxygen plasma the reactive species are not consumed at the bottom of the pillars leading to excessive lateral etching. This effectively removes the whole polyimide layer after prolonged etch times and accidentally releases the silicon mask on top of the polyimide. This behaviour could potentially be exploited for the production of nanoscopic objects like rods, cones or discs by patterning the silicon mask into the desired shape and then releasing them by etching away the polyimide layer instead of using solution growth based methods [34]. The polyimide etch mask after patterning is shown in Fig. 7 resembling a nanoscale forest of "mushroom"-like features caused by minor undercutting.

#### 3.4. Etching of silicon substrate using polyimide mask

Like the polymer sphere material polyimide has a lower etch rate than silicon in the  $SF_6/C_4F_8$  plasma, but unlike in NSL the polyimide etch mask thickness is independent of the feature diameter allowing much higher aspect ratios. By using a three mask process the spheres define the diameter of the pillars whilst the polyimide layer thickness is adjusted to the value necessary to produce the required height of the pillars, thus decoupling lateral and vertical patterning requirements for pillar etching.

The etch process used to transfer the polyimide mask to the substrate is sometimes also referred to as "pseudo"-Bosch process. Passivation gas and etch gas are fed into the chamber at the same time instead of cycling between the two steps producing smoother sidewalls in comparison to the increased sidewall roughness due to the characteristic scalloping in the Bosch process. Silicon pillars with a height of 1.3  $\mu$ m and an average diameter of 75 nm have been produced equating to an aspect ratio of ~17 (Fig. 8). The remaining polyimide mask allowed for further etching but the pillars were ultimately undercut and removed from the substrate. The etch rate of silicon was determined as ~5.5 nm/s while the polyimide etched at a rate of ~1.8 nm/s resulting in a selectivity of roughly 3:1. Fabrication was completed by removing residual polyimide with a short oxygen plasma step.

While for shorter structures the process produces near vertical sidewalls, for taller structures the uniformity of the pillar shape becomes an issue. It appears that after a certain etch depth is reached the passivation gas is not able to penetrate further into the forming pillar array, so that the bottom part of the pillars is not coated with the protective polymer layer. For further etching it may be possible to employ a time multiplexed mixed mode passivating etch to allow more time for the passivating gas to reach to the bottom. Simultaneously the chamber pressure could be adjusted after specific etch depths have been reached to force the passivation gas more into the space between the columns.

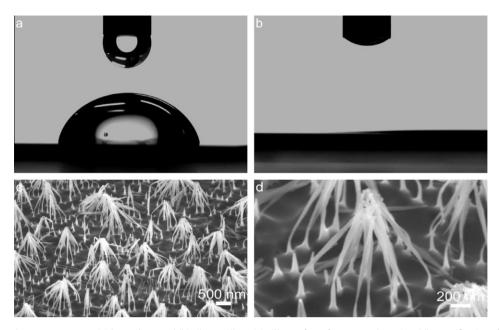

#### 3.5. Characterisation of nanopillars

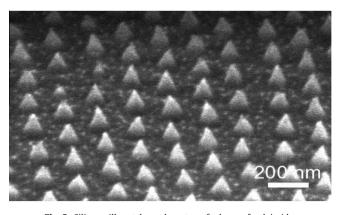

At the moment we are investigating the application of the silicon pillars for surface guiding of liquids. Contact angle measurements on silicon pillar coated substrates were made one week after etching. Samples were stored under ambient conditions in an Entegris chip trav prior to testing. DI water was used to probe the contact angle. They showed a contact angle of almost 0° making these surfaces superhydrophilic. They sustained the contact angle properties for three repeated cycles of drying and wetting with only slight increase to around 4° while IPA cleaned bare silicon samples had an average contact angle of 23° due to native oxide and hydrofluoric acid cleaned samples demonstrated the typical hydrophobic behaviour of pure silicon with contact angles around 80°. Fig. 9a and b shows the contact angle of water on bare silicon and pillar modified surfaces respectively. As mention above, wet processing of the silicon pillars causes them to bundle together at their tops as seen in Fig. 9c and d. An interesting observation was made when the polyimide mask had not been removed prior to wet processing - removal of the top polyimide where the pillars touched did not lead to relaxation of the bent pillars but instead they stayed deformed (Fig. 8d). From this result it is concluded that the silicon pillars have been deformed plastically unlike the polyimide pillars bending under ebeam illumination that returned to their equilibrium shape.

In addition we are exploring the use of the polyimide pillars for the control of cell growth on substrates as polyimide is biocompatible and the flexibility of the pillars should allow for mechanical interaction with the cells, which has been shown to play an important role in cell behaviour on surfaces [35]. Finally the etched samples had distinct colours (red and yellow depending on fabrication conditions) indicating photonic effects worthy of further study.

#### 4. Conclusions

We have introduced a multilayer process into nanosphere lithography for the etching of high aspect ratio silicon pillars utilising a mask stack without the use of complex aspect ratio enhancing etch technology. As a by-product direct patterned high aspectratio polyimide pillars have also been realised using the same approach. The features are easily scalable through variation of etch time and laver thickness. The lateral and vertical dimensions are controlled independently in contrast to standard nanosphere lithography where sphere dimensions put constraints on possible aspect ratio as the spheres erode. Aspect ratios greater then 15 have been achieved using only a standard SF<sub>6</sub> process that does not require complex process chemistry or specialised equipment. Optimisation of the etch process conditions is expected to improve the pillar uniformity and further increase the aspect ratio. Combining the approach with cryo or Bosch processes should potentially lead to aspect ratios never reached before. Unlike in metal-assisted etch processes there is no metal contamination on the pillars allowing integration with CMOS technology. The fabricated structures show interesting properties which we intend to study further. Whilst our pillars showed superhydrophilic properties, other reports on high aspect ratio silicon pillars observed superhydrophobic behaviour. At this time it is not clear whether this is due to differences in the processing method, variations in the pillar diameter – which was significantly smaller in our samples that in other reported work, or due to the bundling behaviour. The structures could find potential application in areas such as surface guiding of liquids, control of light propagation along the surface or guiding of cell growth.

#### Acknowledgements

The authors thank Professor Richard Palmer for use of the Nanoscale Physic Research Laboratory cleanroom facilities. The authors also thank Professor Ian Norton of the School of Chemical Engineering for the use of his contact angle microscope. The authors acknowledge the Birmingham Science City project supported by Advantage West Midlands (AWM) and the European Regional Development Fund (ERDF). The authors further thank the Engineering and Physical Science Research Council (EPSRC) for support.

#### References

- [1] V. Poborchii, T. Tada, T. Kanayama, Appl. Phys. Lett. 82 (4) (2003) 508-510.

- [2] S. Wang, X. Wang, S.P. Jiang, Nanotechnology 19 (2008) 455602.

- [3] S. Turner, L. Kam, M. Issacson, H.G. Craighead, W. Shain, J. Turner, J. Vac. Sci. Technol. B 15 (6) (1997) 2848–2854.

- [4] W.L. Min, P. Jiang, B. Jiang, Adv. Mater. 20 (2008) 3914–3918.

- [5] P.B. Fischer, K. Dai, E. Chen, S.Y. Chou, J. Vac. Sci. Technol. B 11 (6) (1993) 2524– 2527

- [6] M.D. Henry, S. Walavalkar, A. Homyk, A. Scherer, Nanotechnology 20 (2009) 255305.

- [7] H.W. Deckman, J.H. Dunsmuir, Appl. Phys. Lett. 41 (4) (1982) 377-378.

- [8] J.C. Hulteen, R.P. Van Duyne, J. Vac. Sci. Technol. B 13 (1995) 1553-1558.

- [9] A. Wellner, P.R. Preece, J.C. Fowler, R.E. Palmer, Microelectron. Eng. 57–58 (2001) 919–924.

- [10] A.V. Whitney, B.D. Myers, R.P. Van Duyne, Nano Lett. 4 (8) (2004) 1507-1511.

- [11] C.M. Hsu, S.T. Connor, M.X. Tang, Y. Cui, Appl. Phys. Lett. 93 (13) (2008) 133109.

- [12] P.A. Lewis, H. Ahmed, J. Vac. Sci. Technol. B 16 (6) (1998) 2938-2941.

- [13] W. Li, J. Zhou, X.G. Zhang, J. Xu, L. Xu, W. Zhao, P. Sun, F. Song, J. Wan, K. Chen, Nanotechnology 19 (2008) 135308.

- [14] W.L. Min, P. Jiang, B. Jiang, Nanotechnology 19 (2008) 475604.

- [15] X. Zhang, J. Zhang, Z. Ren, X. Li, X. Zhang, D. Zhu, T. Wang, T. Tian, B. Yang, Langmuir 25 (13) (2009) 7375–7382.

- [16] F. Laermer, A. Schilp, German Patent DE-4241045, 1994, US Patent 5501893, 1996.

- [17] C.L. Cheung, R.J. Nikolic, C.E. Reinhardt, T.F. Wang, Nanotechnology 17 (2006) 1339–1343.

- [18] S. Tachi, K. Tsujimoto, S. Okudaira, Appl. Phys. Lett. 52 (8) (1988) 616-618.

- [19] K. Ellinas, A. Smyrnakis, A. Malainou, A. Tserepi, E. Gogolides, Microelectron. Eng. 88 (2011) 2547–2551.

- [20] C.F. Chau, T. Melvin, J. Micromech. Microeng. 18 (2008) 064012.

- [21] G. Sengo, H.A.G.M. von Wolferen, A. Driessen, J. Electrochem. Soc. 158 (10) (2011) H1084.

- [22] H. Struyf, J.F. de Marneffe, D. Goossens, D. Hendrickx, C. Huffman, E. Kunnen, F. Lazzarino, A. Milenin, D. Shamiryan, A. Urbanowicz, A. Vandervorst, W. Boullart, Conf. Proc. AMC XXV: Mat. Res. Soc. (2010) 75–82.

- [23] T. Chevolleau, N. Posseme, T. David, R. Bouyssou, J. Ducote, F. Bailly, M. Darnon, M. El Kodadi, M. Besacier, C. Licitra, M. Guillermet, A. Ostrovsky, C.Verove, O. Joubert, in: Interconnect Technology Conference (IITC), 2010 International, 2010.

- [24] M.M. Hussain, N. Moumen, Z. Zhang, B.F. Womack, J. Electrochem. Soc. 153 (5) (2006) G389.

- [25] S.P. Vaujour, P. Brianceau, C. Comboroure, O. Faynot, Microelectron. Eng. 85 (2008) 800–804.

- [26] D.C. Owe-Yang, T. Yano, T. Ueda, M. Iwabuchi, T. Ogihara, S. Shirai, Proc. SPIE 6923 (2008) 69232I.

- [27] A. Frommhold, J. Manyam, R.E. Palmer, A.P.G. Robinson, Proc. SPIE 8328 (2012) 83280U.

- [28] C.C. Welch, A.L. Goodyear, T. Wahlbrink, M.C. Lemme, T. Mollenhauer, Microelectron. Eng. 83 (2006) 1170–1173.

- [29] H. Li, J. Low, K.S. Brown, N. Wu, IEEE Sens. J. 8 (6) (2008) 880-884.

- [30] J.A. Thornton, Ann. Rev. Mater. Sci. 7 (1977) 239-260.

- [31] K.S. Lau, J. Bico, K.B.K. Teo, M. Chhowalla, G.A.J. Amaratunga, W.I. Milne, G.H. McKinley, K.K. Gleason, Nano Lett. 3 (12) (2003) 1701–1705.

- [32] Y.P. Zhao, J.G. Fan, Appl. Phys. Lett. 88 (2006) 103123.

- [33] Y. Zhang, C.T. Lin, S. Yang, Small 6 (6) (2010) 768-775.

- [34] A.T. Heitsch, C.M. Hessel, V.A. Akhavan, B.A. Korgel, Nano Lett. 9 (8) (2009) 3042–3047.

- [35] K. Franze, J. Guck, Rep. Prog. Phys. 73 (2010) 094601.